载入中...

搜索中...

未找到

#include "hal_spi_v151_regs_def.h"#include "hal_spi_v151_regs_op.h"#include "hal_spi_v151.h"#include "hal_spi.h"#include "osal_interrupt.h"#include "pinctrl.h"#include "lpm_dev_ops.h"#include "chip_io.h"#include "std_def.h"#include "platform_core.h"#include "chip_core_irq.h"#include "arch_port.h"#include "soc_porting.h"#include "spi_porting.h"

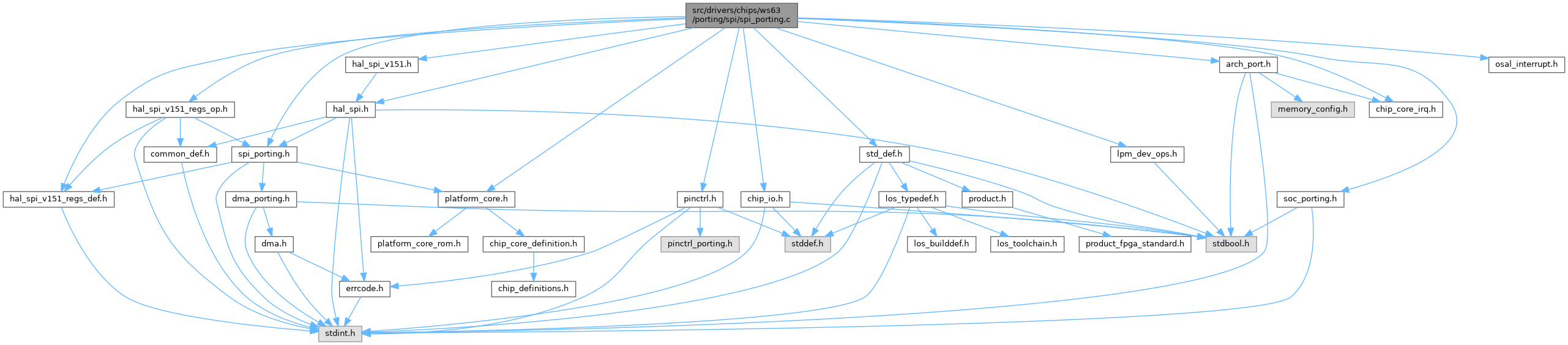

spi_porting.c 的引用(Include)关系图:

结构体 | |

| struct | spi_interrupt |

类型定义 | |

| typedef struct spi_interrupt | hal_spi_interrupt_t |

变量 | |

| spi_v151_regs_t * | g_spi_base_addrs [SPI_BUS_MAX_NUMBER] |

| Base address list for all of the IPs. | |

宏定义说明

◆ CLDO_CRG_CLK_SEL

| #define CLDO_CRG_CLK_SEL 0x44001134 |

◆ CLDO_CRG_DIV_CTL3

| #define CLDO_CRG_DIV_CTL3 0x44001114 |

◆ CLDO_SUB_CRG_CKEN_CTL1

| #define CLDO_SUB_CRG_CKEN_CTL1 0x44001104 |

◆ HAL_QSPI_1_DMA_APP_CORE

| #define HAL_QSPI_1_DMA_APP_CORE 0x0A |

◆ HAL_QSPI_1_DMA_CFG_MASK

| #define HAL_QSPI_1_DMA_CFG_MASK 0x0FU |

◆ HAL_QSPI_1_DMA_DSP_CORE

| #define HAL_QSPI_1_DMA_DSP_CORE 0x0F |

◆ HAL_QSPI_1_DMA_SEC_CORE

| #define HAL_QSPI_1_DMA_SEC_CORE 0x05 |

◆ HAL_QSPI_1_INT_APP_CORE_MASK

| #define HAL_QSPI_1_INT_APP_CORE_MASK (BIT(2)) |

◆ HAL_QSPI_1_INT_SEC_CORE_MASK

| #define HAL_QSPI_1_INT_SEC_CORE_MASK (BIT(0)) |

◆ HAL_QSPI_2_DMA_APP_CORE

| #define HAL_QSPI_2_DMA_APP_CORE 0xA0 |

◆ HAL_QSPI_2_DMA_CFG_MASK

| #define HAL_QSPI_2_DMA_CFG_MASK 0xF0U |

◆ HAL_QSPI_2_DMA_DSP_CORE

| #define HAL_QSPI_2_DMA_DSP_CORE 0xF0 |

◆ HAL_QSPI_2_DMA_SEC_CORE

| #define HAL_QSPI_2_DMA_SEC_CORE 0x50 |

◆ HAL_QSPI_2_INT_APP_CORE_MASK

| #define HAL_QSPI_2_INT_APP_CORE_MASK (BIT(6)) |

◆ HAL_QSPI_2_INT_SEC_CORE_MASK

| #define HAL_QSPI_2_INT_SEC_CORE_MASK (BIT(4)) |

◆ HAL_QSPI_ADDR_LENTH_24

| #define HAL_QSPI_ADDR_LENTH_24 0x06 |

◆ HAL_QSPI_ADDR_LENTH_MAX

| #define HAL_QSPI_ADDR_LENTH_MAX 0x0F |

Address length.

◆ HAL_QSPI_ADDR_LENTH_SHIFT

| #define HAL_QSPI_ADDR_LENTH_SHIFT 0x02 |

◆ HAL_QSPI_CMD_LENTH_8

| #define HAL_QSPI_CMD_LENTH_8 0x02 |

◆ HAL_QSPI_CMD_LENTH_MAX

| #define HAL_QSPI_CMD_LENTH_MAX 0x03 |

Command length.

◆ HAL_QSPI_CMD_LENTH_SHIFT

| #define HAL_QSPI_CMD_LENTH_SHIFT 0x08 |

◆ HAL_QSPI_CTRLR0_REG_MAX

| #define HAL_QSPI_CTRLR0_REG_MAX 0xFFFFFFFF |

SPI_CTRLR0: SPI control register.

◆ HAL_QSPI_DMA_CFG

| #define HAL_QSPI_DMA_CFG (*(volatile unsigned short *)(0x5C000404)) |

◆ HAL_QSPI_INT_CFG

| #define HAL_QSPI_INT_CFG (*(volatile unsigned short *)(0x5C000408)) |

◆ HAL_QSPI_TRANS_TYPES_CMD_S_ADDR_Q

| #define HAL_QSPI_TRANS_TYPES_CMD_S_ADDR_Q 0x01 |

◆ HAL_QSPI_TRANS_TYPES_MAX

| #define HAL_QSPI_TRANS_TYPES_MAX 0x03 |

Trans type.

◆ HAL_QSPI_TRANS_TYPES_SHIFT

| #define HAL_QSPI_TRANS_TYPES_SHIFT 0x00 |

◆ HAL_QSPI_WAIT_CYCLE_2

| #define HAL_QSPI_WAIT_CYCLE_2 0x02 |

◆ HAL_QSPI_WAIT_CYCLE_4

| #define HAL_QSPI_WAIT_CYCLE_4 0x04 |

◆ HAL_QSPI_WAIT_CYCLE_6

| #define HAL_QSPI_WAIT_CYCLE_6 0x06 |

◆ HAL_QSPI_WAIT_CYCLE_MAX

| #define HAL_QSPI_WAIT_CYCLE_MAX 0x1F |

Wait cycles.

◆ HAL_QSPI_WAIT_CYCLE_SHIFT

| #define HAL_QSPI_WAIT_CYCLE_SHIFT 0x0B |

◆ HAL_SPI_ADDR_L_POSE

| #define HAL_SPI_ADDR_L_POSE 2 |

◆ HAL_SPI_BUS_1_DEVICE_MODE_SET_BIT [1/2]

◆ HAL_SPI_BUS_1_DEVICE_MODE_SET_BIT [2/2]

◆ HAL_SPI_BUS_1_DEVICE_MODE_SET_BIT_MAX [1/2]

| #define HAL_SPI_BUS_1_DEVICE_MODE_SET_BIT_MAX 0x01 |

◆ HAL_SPI_BUS_1_DEVICE_MODE_SET_BIT_MAX [2/2]

| #define HAL_SPI_BUS_1_DEVICE_MODE_SET_BIT_MAX 0x01 |

◆ HAL_SPI_BUS_1_DEVICE_MODE_SET_BIT_SHIFT [1/2]

| #define HAL_SPI_BUS_1_DEVICE_MODE_SET_BIT_SHIFT 0x00 |

◆ HAL_SPI_BUS_1_DEVICE_MODE_SET_BIT_SHIFT [2/2]

| #define HAL_SPI_BUS_1_DEVICE_MODE_SET_BIT_SHIFT 0x00 |

◆ HAL_SPI_BUS_2_DEVICE_MODE_MASTER [1/2]

| #define HAL_SPI_BUS_2_DEVICE_MODE_MASTER 0x01 |

◆ HAL_SPI_BUS_2_DEVICE_MODE_MASTER [2/2]

| #define HAL_SPI_BUS_2_DEVICE_MODE_MASTER 0x01 |

◆ HAL_SPI_BUS_2_DEVICE_MODE_SET_BIT_MAX [1/2]

| #define HAL_SPI_BUS_2_DEVICE_MODE_SET_BIT_MAX 0x01 |

◆ HAL_SPI_BUS_2_DEVICE_MODE_SET_BIT_MAX [2/2]

| #define HAL_SPI_BUS_2_DEVICE_MODE_SET_BIT_MAX 0x01 |

◆ HAL_SPI_BUS_2_DEVICE_MODE_SET_BIT_SHIFT [1/2]

| #define HAL_SPI_BUS_2_DEVICE_MODE_SET_BIT_SHIFT 0x01 |

◆ HAL_SPI_BUS_2_DEVICE_MODE_SET_BIT_SHIFT [2/2]

| #define HAL_SPI_BUS_2_DEVICE_MODE_SET_BIT_SHIFT 0x01 |

◆ HAL_SPI_BUS_MAX_NUM

| #define HAL_SPI_BUS_MAX_NUM (SPI_BUS_MAX_NUMBER) |

◆ HAL_SPI_BUSY_FLAG

| #define HAL_SPI_BUSY_FLAG (BIT(0)) |

◆ HAL_SPI_CE_LIN_TOGGLE_ENABLE

| #define HAL_SPI_CE_LIN_TOGGLE_ENABLE (BIT(24)) |

◆ HAL_SPI_CLK_DIV_2

| #define HAL_SPI_CLK_DIV_2 2 |

◆ HAL_SPI_CLK_DIV_20

| #define HAL_SPI_CLK_DIV_20 20 |

◆ HAL_SPI_CLK_DIV_4

| #define HAL_SPI_CLK_DIV_4 4 |

◆ HAL_SPI_CLK_DIV_REG_MAX

| #define HAL_SPI_CLK_DIV_REG_MAX 0xFFFF |

BAUDR : Baud rate select.

◆ HAL_SPI_CLKS_MODE_MAX

| #define HAL_SPI_CLKS_MODE_MAX 0x03 |

CLOCK : SCPOL and SCPH.

◆ HAL_SPI_CLKS_MODE_SHIFT

| #define HAL_SPI_CLKS_MODE_SHIFT 0x06 |

◆ HAL_SPI_CTRLR0_REG_MAX

| #define HAL_SPI_CTRLR0_REG_MAX 0xFFFFFFFF |

◆ HAL_SPI_DATA_FRAME_SIZE_BIT

| #define HAL_SPI_DATA_FRAME_SIZE_BIT 16 |

◆ HAL_SPI_DATA_FRAME_SIZE_BITFILD

| #define HAL_SPI_DATA_FRAME_SIZE_BITFILD 5 |

◆ HAL_SPI_DDR_EN

| #define HAL_SPI_DDR_EN BIT(16) |

◆ HAL_SPI_DR_REG_SIZE

| #define HAL_SPI_DR_REG_SIZE 36 |

◆ HAL_SPI_ENABLE

| #define HAL_SPI_ENABLE 0x01 |

SSIENR : SSI enable register.

◆ HAL_SPI_FRAME_FORMAT_MAX

| #define HAL_SPI_FRAME_FORMAT_MAX 0x03 |

FRF : Frame format.

◆ HAL_SPI_FRAME_FORMAT_SHIFT

| #define HAL_SPI_FRAME_FORMAT_SHIFT 0x15 |

◆ HAL_SPI_FRAME_SIZE_16

| #define HAL_SPI_FRAME_SIZE_16 0x0F |

◆ HAL_SPI_FRAME_SIZE_32

| #define HAL_SPI_FRAME_SIZE_32 0x1F |

◆ HAL_SPI_FRAME_SIZE_8

| #define HAL_SPI_FRAME_SIZE_8 0x07 |

◆ HAL_SPI_FRAME_SIZE_MAX

| #define HAL_SPI_FRAME_SIZE_MAX 0x1F |

DFS : Data frame size.

◆ HAL_SPI_FRAME_SIZE_SHIFT

| #define HAL_SPI_FRAME_SIZE_SHIFT 0x10 |

◆ hal_spi_frame_size_trans_to_frame_bytes

| #define hal_spi_frame_size_trans_to_frame_bytes | ( | x | ) | (((x) + 1) >> 0x03) |

◆ HAL_SPI_INST_DDR_EN

| #define HAL_SPI_INST_DDR_EN BIT(17) |

◆ HAL_SPI_INST_L_POSE

| #define HAL_SPI_INST_L_POSE 8 |

◆ HAL_SPI_INTERRUPT_REG_MAX

| #define HAL_SPI_INTERRUPT_REG_MAX 0x3F |

IMR : Interrupt mask register.

◆ HAL_SPI_MAXIMUM_CLK_DIV

| #define HAL_SPI_MAXIMUM_CLK_DIV 65534 |

◆ hal_spi_mhz_to_hz

| #define hal_spi_mhz_to_hz | ( | x | ) | ((x) * 1000000) |

◆ HAL_SPI_MINUMUM_CLK_DIV

| #define HAL_SPI_MINUMUM_CLK_DIV 2 |

◆ HAL_SPI_RECEIVED_DATA_REG_MAX

| #define HAL_SPI_RECEIVED_DATA_REG_MAX 0xFFFF |

CTRLR1 : Control register 1.

◆ HAL_SPI_RSVD_NONE

| #define HAL_SPI_RSVD_NONE 0 |

◆ HAL_SPI_RSVD_X16

| #define HAL_SPI_RSVD_X16 0x11 |

◆ HAL_SPI_RSVD_X8

| #define HAL_SPI_RSVD_X8 0 |

◆ HAL_SPI_RSVD_X8_X8

| #define HAL_SPI_RSVD_X8_X8 1 |

◆ HAL_SPI_RX_FIFO_FULL_FLAG

| #define HAL_SPI_RX_FIFO_FULL_FLAG (BIT(4)) |

SR : Status register.

◆ HAL_SPI_RX_FIFO_NOT_EMPTY_FLAG

| #define HAL_SPI_RX_FIFO_NOT_EMPTY_FLAG (BIT(3)) |

◆ HAL_SPI_RX_SAMPLE_DLY_MAX

| #define HAL_SPI_RX_SAMPLE_DLY_MAX 0xFF |

◆ HAL_SPI_RX_SAMPLE_DLY_SHIFT

| #define HAL_SPI_RX_SAMPLE_DLY_SHIFT 0 |

◆ HAL_SPI_RXDS_EN

| #define HAL_SPI_RXDS_EN BIT(18) |

◆ HAL_SPI_SLAVE_ENABLE_REG_MAX

| #define HAL_SPI_SLAVE_ENABLE_REG_MAX 0xFFFFFFFF |

SER : Slave enable register.

◆ HAL_SPI_TRANS_MODE_EEPROM

| #define HAL_SPI_TRANS_MODE_EEPROM 0x03 |

◆ HAL_SPI_TRANS_MODE_MAX

| #define HAL_SPI_TRANS_MODE_MAX 0x03 |

TMOD : Trans mode.

◆ HAL_SPI_TRANS_MODE_RX

| #define HAL_SPI_TRANS_MODE_RX 0x02 |

◆ HAL_SPI_TRANS_MODE_SHIFT

| #define HAL_SPI_TRANS_MODE_SHIFT 0x08 |

◆ HAL_SPI_TRANS_MODE_TX

| #define HAL_SPI_TRANS_MODE_TX 0x01 |

◆ HAL_SPI_TRANS_MODE_TXRX

| #define HAL_SPI_TRANS_MODE_TXRX 0x00 |

◆ HAL_SPI_TX_FIFO_EMPTY_FLAG

| #define HAL_SPI_TX_FIFO_EMPTY_FLAG (BIT(2)) |

◆ HAL_SPI_TX_FIFO_NOT_FULL_FLAG

| #define HAL_SPI_TX_FIFO_NOT_FULL_FLAG (BIT(1)) |

◆ PLL_CLK480M

| #define PLL_CLK480M 480 |

◆ QSPI_DMA_TX_DATA_LEVEL_8

| #define QSPI_DMA_TX_DATA_LEVEL_8 8 |

◆ SPI_DIV_LEN

| #define SPI_DIV_LEN 5 |

◆ SPI_DMA_TX_DATA_LEVEL_4

| #define SPI_DMA_TX_DATA_LEVEL_4 4 |

类型定义说明

◆ hal_spi_interrupt_t

| typedef struct spi_interrupt hal_spi_interrupt_t |

函数说明

◆ hal_opi_cmd_trans_mode()

| void hal_opi_cmd_trans_mode | ( | spi_bus_t | bus, |

| uint32_t | mode | ||

| ) |

◆ hal_opi_ddr_en()

| void hal_opi_ddr_en | ( | spi_bus_t | bus, |

| bool | on | ||

| ) |

◆ hal_opi_disable()

| bool hal_opi_disable | ( | spi_bus_t | bus | ) |

◆ hal_opi_disable_slave()

| void hal_opi_disable_slave | ( | spi_bus_t | bus | ) |

◆ hal_opi_dma_control()

| bool hal_opi_dma_control | ( | spi_bus_t | bus, |

| hal_spi_dma_control_t | operation | ||

| ) |

◆ hal_opi_enable()

| bool hal_opi_enable | ( | spi_bus_t | bus | ) |

◆ hal_opi_is_busy()

| bool hal_opi_is_busy | ( | spi_bus_t | bus | ) |

◆ hal_opi_read_data()

| uint32_t hal_opi_read_data | ( | spi_bus_t | bus | ) |

◆ hal_opi_reset_config()

| bool hal_opi_reset_config | ( | spi_bus_t | bus | ) |

◆ hal_opi_rx_fifo_is_full()

| bool hal_opi_rx_fifo_is_full | ( | spi_bus_t | bus | ) |

◆ hal_opi_rx_fifo_is_not_empty()

| bool hal_opi_rx_fifo_is_not_empty | ( | spi_bus_t | bus | ) |

◆ hal_opi_select_slave()

| bool hal_opi_select_slave | ( | spi_bus_t | bus, |

| uint32_t | slave_num | ||

| ) |

◆ hal_opi_set_addr_len()

| void hal_opi_set_addr_len | ( | spi_bus_t | bus, |

| hal_spi_addr_len_t | addr_len | ||

| ) |

◆ hal_opi_set_dma_rx_data_level()

| bool hal_opi_set_dma_rx_data_level | ( | spi_bus_t | bus, |

| uint32_t | data_level | ||

| ) |

◆ hal_opi_set_fifo_threshold()

| bool hal_opi_set_fifo_threshold | ( | spi_bus_t | bus, |

| uint32_t | threshold | ||

| ) |

◆ hal_opi_set_frame_format()

| bool hal_opi_set_frame_format | ( | spi_bus_t | bus, |

| hal_spi_frame_format_t | frame_format | ||

| ) |

◆ hal_opi_set_frame_size()

| bool hal_opi_set_frame_size | ( | spi_bus_t | bus, |

| uint32_t | frame_size | ||

| ) |

◆ hal_opi_set_freq()

| bool hal_opi_set_freq | ( | spi_bus_t | bus, |

| uint32_t | clk_in_mhz | ||

| ) |

◆ hal_opi_set_inst_len()

| void hal_opi_set_inst_len | ( | spi_bus_t | bus, |

| hal_spi_inst_len_t | inst_len | ||

| ) |

◆ hal_opi_set_received_data_num()

| bool hal_opi_set_received_data_num | ( | spi_bus_t | bus, |

| uint32_t | number | ||

| ) |

◆ hal_opi_set_rx_sample_dly()

| bool hal_opi_set_rx_sample_dly | ( | spi_bus_t | bus, |

| uint8_t | delay | ||

| ) |

◆ hal_opi_set_trans_mode()

| bool hal_opi_set_trans_mode | ( | spi_bus_t | bus, |

| uint32_t | tmod | ||

| ) |

◆ hal_opi_set_trans_type()

| bool hal_opi_set_trans_type | ( | spi_bus_t | bus, |

| hal_spi_trans_type_t | trans_type | ||

| ) |

◆ hal_opi_set_tx_fifo_threshold()

| bool hal_opi_set_tx_fifo_threshold | ( | spi_bus_t | bus, |

| uint32_t | threshold | ||

| ) |

◆ hal_opi_tx_fifo_is_empty()

| bool hal_opi_tx_fifo_is_empty | ( | spi_bus_t | bus | ) |

◆ hal_opi_tx_fifo_is_not_full()

| bool hal_opi_tx_fifo_is_not_full | ( | spi_bus_t | bus | ) |

◆ hal_opi_write_data()

| bool hal_opi_write_data | ( | spi_bus_t | bus, |

| uint32_t | data | ||

| ) |

◆ hal_qspi_set_wait_cycles()

| bool hal_qspi_set_wait_cycles | ( | spi_bus_t | bus, |

| uint32_t | wait_cyc | ||

| ) |