载入中...

搜索中...

未找到

#include <los_task.h>#include "errcode.h"#include "chip_io.h"#include "osal_types.h"#include "soc_osal.h"#include "arch_barrier.h"#include "debug_print.h"#include "tcxo.h"#include "timer.h"#include "timer_porting.h"#include "soc_porting.h"#include "uart.h"#include "uart_porting.h"#include "dma.h"#include "gpio.h"#include "efuse.h"#include "tsensor.h"#include "watchdog.h"#include "clock_init.h"#include "security_init.h"#include "pinctrl.h"#include "main.h"#include "wifi_device.h"#include "hal_watchdog_v151_regs_op.h"#include "hal_watchdog.h"#include "radar_service.h"#include "reboot_porting.h"#include "pm_porting.h"

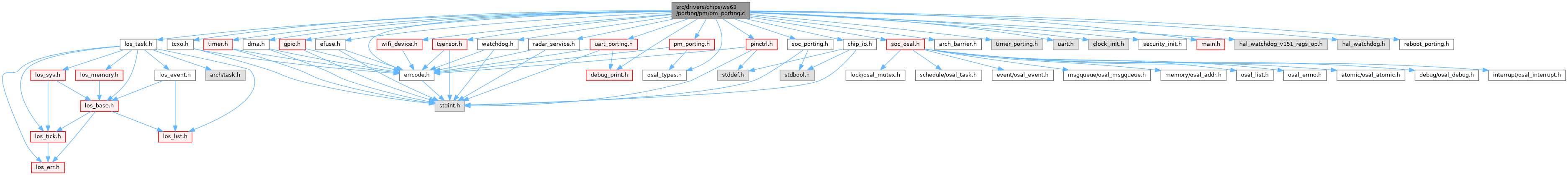

pm_porting.c 的引用(Include)关系图:

枚举 | |

| enum | pm_crg_record_index_t { PM_CRG_CKEN_CTL0 = 0 , PM_CRG_CKEN_CTL1 , PM_CRG_RST_CTL0 , PM_CRG_RST_CTL1 , PM_CRG_RECORD_MAX } |

函数 | |

| void | pm_port_open_rf (void) |

| void | pm_port_close_rf (void) |

| void | pm_port_open_wifi_sub (void) |

| void | pm_port_close_wifi_sub (void) |

| void | pm_port_open_bt_sub (void) |

| void | pm_port_close_bt_sub (void) |

| void | pm_port_open_wifi_hw (void) |

| void | pm_port_close_wifi_hw (void) |

| void | pm_port_open_bt_hw (void) |

| void | pm_port_close_bt_hw (void) |

| int | pm_port_flash_sem_down (void) |

| void | pm_port_flash_sem_up (void) |

| int | pm_port_dma_sem_down (void) |

| void | pm_port_dma_sem_up (void) |

| void | pm_port_pm_hook_cb_register (uint32_t hook, pm_hook_cb_t cb) |

| void | pm_port_enter_lowpower_prepare_cb_default (void) |

| void | pm_port_enter_lowpower_finish_cb_default (void) |

| void | pm_port_exit_lowpower_prepare_cb_default (void) |

| void | pm_port_exit_lowpower_finish_cb_default (void) |

| void | pm_port_enter_lowpower (void) |

| void | pm_port_exit_lowpower (void) |

| void | pm_porting_wait_exit_lowpower (void) |

变量 | |

| uint32_t | g_pm_iocfg_sel_record [15] = {} |

| uint32_t | g_pm_iocfg_pad_record [15] = {} |

| uint32_t | g_pm_crg_record [PM_CRG_RECORD_MAX] = {} |

| uint32_t | g_pm_uart_clock_record [UART_BUS_MAX_NUMBER] = {} |

| uint32_t | g_pm_wdt_timeout = 0 |

| uint32_t | g_pm_wdt_mode = 0 |

| pm_hook_cb_t | g_pm_hook_cb_list [PM_HOOK_MAX_NUM] |

| bool | g_pm_is_wifi_hw_open = true |

| bool | g_pm_is_bt_hw_open = true |

| bool | g_pm_is_in_lowpower = false |

| bool | g_pm_is_in_process = false |

| osal_semaphore * | g_flash_sem = NULL |

| osal_semaphore * | g_dma_sem = NULL |

宏定义说明

◆ CLDO_CRG_CLK_SEL

| #define CLDO_CRG_CLK_SEL 0x44001134 |

◆ CLDO_CRG_DIV_CTL0

| #define CLDO_CRG_DIV_CTL0 0x44001108 |

◆ CLOCK_24MHZ

| #define CLOCK_24MHZ 0x1 |

◆ CLOCK_MASK

| #define CLOCK_MASK 0x1 |

◆ CMU_CLK_24M_USB

| #define CMU_CLK_24M_USB 0x40003454 |

◆ CMU_CLK_320M_WDBB

| #define CMU_CLK_320M_WDBB 0x40003448 |

◆ CMU_CLK_480M_WDBB

| #define CMU_CLK_480M_WDBB 0x4000344c |

◆ EFUSE_24M_CLOCK_PERIOD

| #define EFUSE_24M_CLOCK_PERIOD 0x29 |

◆ EFUSE_40M_CLOCK_PERIOD

| #define EFUSE_40M_CLOCK_PERIOD 0x19 |

◆ EFUSE_BOOT_DONE_MASK

| #define EFUSE_BOOT_DONE_MASK 0x4 |

◆ EFUSE_CLOCK_PERIOD

| #define EFUSE_CLOCK_PERIOD 0x44008034 |

◆ EFUSE_STS

| #define EFUSE_STS 0x4400802c |

◆ EXCEP_RO_RG

| #define EXCEP_RO_RG 0x4000319c |

◆ FNPLL_LOCK_QUERY_DELAY_MS

| #define FNPLL_LOCK_QUERY_DELAY_MS 1 |

◆ FNPLL_LOCK_QUERY_TIMES

| #define FNPLL_LOCK_QUERY_TIMES 30 |

◆ FNPLL_LOCK_RETRY_DELAY_US

| #define FNPLL_LOCK_RETRY_DELAY_US 2 |

◆ FNPLL_LOCK_RETRY_TIMES

| #define FNPLL_LOCK_RETRY_TIMES 3 |

◆ HW_CTL

| #define HW_CTL 0x40000014 |

◆ IOCFG_RECORD_NUM

| #define IOCFG_RECORD_NUM 15 |

◆ MAX_RETRY_TIMES

| #define MAX_RETRY_TIMES 50 |

◆ PLL_CLOCK_160M

| #define PLL_CLOCK_160M 160000000 |

◆ PLL_LOCKED

| #define PLL_LOCKED 1 |

◆ PLL_UNLOCKED

| #define PLL_UNLOCKED 0 |

◆ PM_DMA_SEM_INIT_CNT

| #define PM_DMA_SEM_INIT_CNT 1 |

◆ PM_ENTER_LOWPOWER_WFI_DELAY_MS

| #define PM_ENTER_LOWPOWER_WFI_DELAY_MS 200 |

◆ PM_FLASH_SEM_INIT_CNT

| #define PM_FLASH_SEM_INIT_CNT 1 |

◆ PM_WAIT_EXIT_LOWPOWER_MS

| #define PM_WAIT_EXIT_LOWPOWER_MS 100 |

◆ PM_WAIT_FLASH_WORK_DOWN_MS

| #define PM_WAIT_FLASH_WORK_DOWN_MS 10 |

◆ PMU_PROCESS_DELAY_US

| #define PMU_PROCESS_DELAY_US 10 |

◆ PMU_RF_OPEN_DELAY_US

| #define PMU_RF_OPEN_DELAY_US 120 |

◆ REG_ADDR_INTERVAL

| #define REG_ADDR_INTERVAL 0x4 |

◆ REG_AON_CRG_CKEN_CTL

| #define REG_AON_CRG_CKEN_CTL 0x40002100 |

Copyright (c) HiSilicon (Shanghai) Technologies Co., Ltd. 2023-2023. All rights reserved.

Description: Provide pm port source.

History:

2023-11-13, Create file.

◆ REG_AON_SOFT_RST_CTL

| #define REG_AON_SOFT_RST_CTL 0x40002110 |

◆ REG_CLDO_CRG_CLK_SEL

| #define REG_CLDO_CRG_CLK_SEL 0x44001134 |

◆ REG_CLDO_CRG_DIV_CTL0

| #define REG_CLDO_CRG_DIV_CTL0 0x44001108 |

◆ REG_CLDO_CRG_DIV_CTL7

| #define REG_CLDO_CRG_DIV_CTL7 0x44001124 |

◆ REG_CLDO_CRG_RST_SOFT_CFG0

| #define REG_CLDO_CRG_RST_SOFT_CFG0 0x44001138 |

◆ REG_CLDO_CRG_RST_SOFT_CFG1

| #define REG_CLDO_CRG_RST_SOFT_CFG1 0x4400113C |

◆ REG_CLDO_SUB_CRG_CKEN_CTL0

| #define REG_CLDO_SUB_CRG_CKEN_CTL0 0x44001100 |

◆ REG_CLDO_SUB_CRG_CKEN_CTL1

| #define REG_CLDO_SUB_CRG_CKEN_CTL1 0x44001104 |

◆ REG_CMU_CLK_480M_WDBB

| #define REG_CMU_CLK_480M_WDBB 0x4000344C |

◆ REG_CMU_FBDIV

| #define REG_CMU_FBDIV 0x40003430 |

◆ REG_CMU_FNPLL_SIG

| #define REG_CMU_FNPLL_SIG 0x4000342C |

◆ REG_CMU_FRAC

| #define REG_CMU_FRAC 0x40003434 |

◆ REG_EXCEP_RO_RG

| #define REG_EXCEP_RO_RG 0x4000319C |

◆ REG_FNPLL_CFG0

| #define REG_FNPLL_CFG0 0x4000340C |

◆ REG_FNPLL_CFG1

| #define REG_FNPLL_CFG1 0x40003410 |

◆ REG_FNPLL_CFG2

| #define REG_FNPLL_CFG2 0x40003414 |

◆ REG_FNPLL_CFG3

| #define REG_FNPLL_CFG3 0x40003418 |

◆ REG_FNPLL_CFG4

| #define REG_FNPLL_CFG4 0x4000341C |

◆ REG_FNPLL_CFG5

| #define REG_FNPLL_CFG5 0x40003420 |

◆ REG_GPIO_PAD_START_ADDR

| #define REG_GPIO_PAD_START_ADDR 0x4400D800 |

◆ REG_GPIO_SEL_START_ADDR

| #define REG_GPIO_SEL_START_ADDR 0x4400D000 |

◆ REG_ISO_SIG

| #define REG_ISO_SIG 0x40003230 |

◆ REG_PMU_ABBLDO_1P0

| #define REG_PMU_ABBLDO_1P0 0x40003144 |

◆ REG_PMU_CMULDO1_0P9

| #define REG_PMU_CMULDO1_0P9 0x4000312C |

◆ REG_PMU_LNALDO_1P0

| #define REG_PMU_LNALDO_1P0 0x40003138 |

◆ REG_PMU_PHY_LDO

| #define REG_PMU_PHY_LDO 0x4000316C |

◆ REG_PMU_PLLLDO_1P0

| #define REG_PMU_PLLLDO_1P0 0x40003148 |

◆ REG_PMU_RXLDO_1P0

| #define REG_PMU_RXLDO_1P0 0x40003134 |

◆ REG_PMU_TXLDO_1P8

| #define REG_PMU_TXLDO_1P8 0x40003168 |

◆ REG_PMU_VCOLDO_1P0

| #define REG_PMU_VCOLDO_1P0 0x40003140 |

◆ REG_WDT_CR

| #define REG_WDT_CR 0x40006010 |

◆ RF_PLL_LOCK_DELAY_US

| #define RF_PLL_LOCK_DELAY_US 100 |

◆ TCXO_CLOCK_24M

| #define TCXO_CLOCK_24M 24000000 |

◆ TCXO_CLOCK_40M

| #define TCXO_CLOCK_40M 40000000 |

◆ UART0_RXD_SEL

| #define UART0_RXD_SEL 0x4400d048 |

◆ UART1_RXD_SEL

| #define UART1_RXD_SEL 0x4400d040 |

◆ UART2_RXD_SEL

| #define UART2_RXD_SEL 0x4400d01c |

◆ UART_0_MODE

| #define UART_0_MODE 1 |

◆ UART_1_MODE

| #define UART_1_MODE 1 |

◆ UART_2_MODE

| #define UART_2_MODE 2 |

◆ UART_PRINT_DELAY_MS

| #define UART_PRINT_DELAY_MS 10 |

◆ VAL_GPIO_PAD_DEFAULT

| #define VAL_GPIO_PAD_DEFAULT 0x800 |

◆ VAL_GPIO_SEL_DEFAULT

| #define VAL_GPIO_SEL_DEFAULT 0x0 |

◆ WDT_TIMEOUT_S

| #define WDT_TIMEOUT_S 15 |

◆ WIFI_BLE_HW_PROCESS_DELAY_US

| #define WIFI_BLE_HW_PROCESS_DELAY_US 10 |

◆ WKUP_UART

| #define WKUP_UART CONFIG_PM_SUPPORT_WKUP_UART |

枚举类型说明

◆ pm_crg_record_index_t

函数说明

◆ pm_port_close_bt_hw()

| void pm_port_close_bt_hw | ( | void | ) |

◆ pm_port_close_bt_sub()

| void pm_port_close_bt_sub | ( | void | ) |

◆ pm_port_close_rf()

| void pm_port_close_rf | ( | void | ) |

◆ pm_port_close_wifi_hw()

| void pm_port_close_wifi_hw | ( | void | ) |

◆ pm_port_close_wifi_sub()

| void pm_port_close_wifi_sub | ( | void | ) |

◆ pm_port_dma_sem_down()

| int pm_port_dma_sem_down | ( | void | ) |

◆ pm_port_dma_sem_up()

| void pm_port_dma_sem_up | ( | void | ) |

◆ pm_port_enter_lowpower()

| void pm_port_enter_lowpower | ( | void | ) |

◆ pm_port_enter_lowpower_finish_cb_default()

| void pm_port_enter_lowpower_finish_cb_default | ( | void | ) |

◆ pm_port_enter_lowpower_prepare_cb_default()

| void pm_port_enter_lowpower_prepare_cb_default | ( | void | ) |

◆ pm_port_exit_lowpower()

| void pm_port_exit_lowpower | ( | void | ) |

◆ pm_port_exit_lowpower_finish_cb_default()

| void pm_port_exit_lowpower_finish_cb_default | ( | void | ) |

◆ pm_port_exit_lowpower_prepare_cb_default()

| void pm_port_exit_lowpower_prepare_cb_default | ( | void | ) |

◆ pm_port_flash_sem_down()

| int pm_port_flash_sem_down | ( | void | ) |

◆ pm_port_flash_sem_up()

| void pm_port_flash_sem_up | ( | void | ) |

◆ pm_port_open_bt_hw()

| void pm_port_open_bt_hw | ( | void | ) |

◆ pm_port_open_bt_sub()

| void pm_port_open_bt_sub | ( | void | ) |

◆ pm_port_open_rf()

| void pm_port_open_rf | ( | void | ) |

◆ pm_port_open_wifi_hw()

| void pm_port_open_wifi_hw | ( | void | ) |

◆ pm_port_open_wifi_sub()

| void pm_port_open_wifi_sub | ( | void | ) |

◆ pm_port_pm_hook_cb_register()

| void pm_port_pm_hook_cb_register | ( | uint32_t | hook, |

| pm_hook_cb_t | cb | ||

| ) |

◆ pm_porting_wait_exit_lowpower()

| void pm_porting_wait_exit_lowpower | ( | void | ) |

变量说明

◆ g_dma_sem

| osal_semaphore* g_dma_sem = NULL |

◆ g_flash_sem

| osal_semaphore* g_flash_sem = NULL |

◆ g_pm_crg_record

| uint32_t g_pm_crg_record[PM_CRG_RECORD_MAX] = {} |

◆ g_pm_hook_cb_list

| pm_hook_cb_t g_pm_hook_cb_list[PM_HOOK_MAX_NUM] |

初始值:

= {

}

void pm_port_exit_lowpower_prepare_cb_default(void)

Definition pm_porting.c:593

void pm_port_enter_lowpower_prepare_cb_default(void)

Definition pm_porting.c:515

void pm_port_exit_lowpower_finish_cb_default(void)

Definition pm_porting.c:616

void pm_port_enter_lowpower_finish_cb_default(void)

Definition pm_porting.c:558

◆ g_pm_iocfg_pad_record

| uint32_t g_pm_iocfg_pad_record[15] = {} |

◆ g_pm_iocfg_sel_record

| uint32_t g_pm_iocfg_sel_record[15] = {} |

◆ g_pm_is_bt_hw_open

| bool g_pm_is_bt_hw_open = true |

◆ g_pm_is_in_lowpower

| bool g_pm_is_in_lowpower = false |

◆ g_pm_is_in_process

| bool g_pm_is_in_process = false |

◆ g_pm_is_wifi_hw_open

| bool g_pm_is_wifi_hw_open = true |

◆ g_pm_uart_clock_record

| uint32_t g_pm_uart_clock_record[UART_BUS_MAX_NUMBER] = {} |

◆ g_pm_wdt_mode

| uint32_t g_pm_wdt_mode = 0 |

◆ g_pm_wdt_timeout

| uint32_t g_pm_wdt_timeout = 0 |