载入中...

搜索中...

未找到

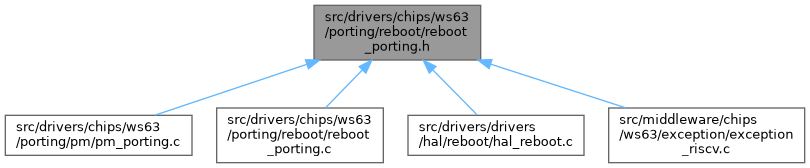

此图展示该文件直接或间接的被哪些文件引用了:

类型定义 | |

| typedef enum reboot_port_rst_reason | reboot_port_rst_reason_t |

枚举 | |

| enum | reboot_port_rst_reason { RST_REASON_WDT_RST = 0 , RST_REASON_SOFT_RST , RST_REASON_HARD_RST , RST_REASON_INVALID } |

函数 | |

| void | reboot_port_reboot_chip (void) |

| uint32_t | reboot_port_get_rst_reason (void) |

| void | reboot_mem_flash_erase (void) |

| void | reboot_mem_save_to_flash (void) |

宏定义说明

◆ HAL_BCPU_RESET_STS_REG

| #define HAL_BCPU_RESET_STS_REG (GLB_CTL_M_RB_BASE + 0x30) |

◆ HAL_CHIP_RESET_REG

| #define HAL_CHIP_RESET_REG (GLB_CTL_M_RB_BASE + CHIP_RESET_OFF) |

◆ HAL_CHIP_RESET_REG_ENABLE_RESET_BIT

| #define HAL_CHIP_RESET_REG_ENABLE_RESET_BIT 2 |

◆ HAL_CHIP_RESET_REG_OFFSET

| #define HAL_CHIP_RESET_REG_OFFSET 0x0 |

◆ HAL_DSP_RESET_STS_REG

| #define HAL_DSP_RESET_STS_REG (GLB_CTL_B_RB_BASE + 0x38) |

◆ HAL_MCPU_RESET_STS_REG

| #define HAL_MCPU_RESET_STS_REG (GLB_CTL_M_RB_BASE + 0x34) |

◆ HAL_PMU_PROTECT_BUCK1_SCP_BIT

| #define HAL_PMU_PROTECT_BUCK1_SCP_BIT 3 |

◆ HAL_PMU_PROTECT_BUCK2_SCP_BIT

| #define HAL_PMU_PROTECT_BUCK2_SCP_BIT 2 |

◆ HAL_PMU_PROTECT_CHIP_WDG_BIT

| #define HAL_PMU_PROTECT_CHIP_WDG_BIT 4 |

◆ HAL_PMU_PROTECT_CHIP_WDG_BIT_CLR

| #define HAL_PMU_PROTECT_CHIP_WDG_BIT_CLR 0 |

◆ HAL_PMU_PROTECT_STATUS_CLR_REG

| #define HAL_PMU_PROTECT_STATUS_CLR_REG (PMU1_CTL_RB_BASE + 0x370) |

◆ HAL_PMU_PROTECT_STATUS_REG

| #define HAL_PMU_PROTECT_STATUS_REG (PMU1_CTL_RB_BASE + 0x370) |

◆ HAL_REBOOT_REASON_BCPU_CHIP_WDT

| #define HAL_REBOOT_REASON_BCPU_CHIP_WDT 0x8004 |

◆ HAL_REBOOT_REASON_BCPU_WDT

| #define HAL_REBOOT_REASON_BCPU_WDT 0x8002 |

◆ HAL_REBOOT_REASON_DSP_WDT

| #define HAL_REBOOT_REASON_DSP_WDT 0x4002 |

◆ HAL_REBOOT_REASON_MCPU_WDT

| #define HAL_REBOOT_REASON_MCPU_WDT 0x2002 |

Copyright (c) HiSilicon (Shanghai) Technologies Co., Ltd. 2022-2022. All rights reserved.

Description: Provides pmp port template

History:

2022-09-26, Create file.

◆ HAL_RESET_STS_CLEAR_ALL

| #define HAL_RESET_STS_CLEAR_ALL 0xFF |

◆ HAL_RESET_STS_CLEAR_REG

| #define HAL_RESET_STS_CLEAR_REG (GLB_CTL_M_RB_BASE + 0x3c) |

◆ HAL_RESET_STS_COMMON_RESET_BIT

| #define HAL_RESET_STS_COMMON_RESET_BIT 0 |

◆ HAL_RESET_STS_CORE_RESET_BIT

| #define HAL_RESET_STS_CORE_RESET_BIT 1 |

◆ HAL_RESET_STS_CORE_WDT_RESET_BIT

| #define HAL_RESET_STS_CORE_WDT_RESET_BIT 2 |

◆ HAL_ULP_AON_GENERAL_REG

| #define HAL_ULP_AON_GENERAL_REG (ULP_AON_CTL_RB_ADDR + 0x14) |

◆ HAL_ULP_AON_NO_POWEROFF_FLAG

| #define HAL_ULP_AON_NO_POWEROFF_FLAG 0xA5A5 |