载入中...

搜索中...

未找到

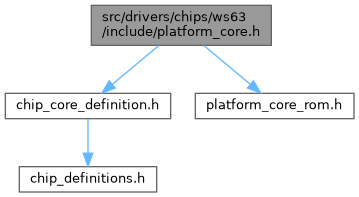

platform_core.h 的引用(Include)关系图:

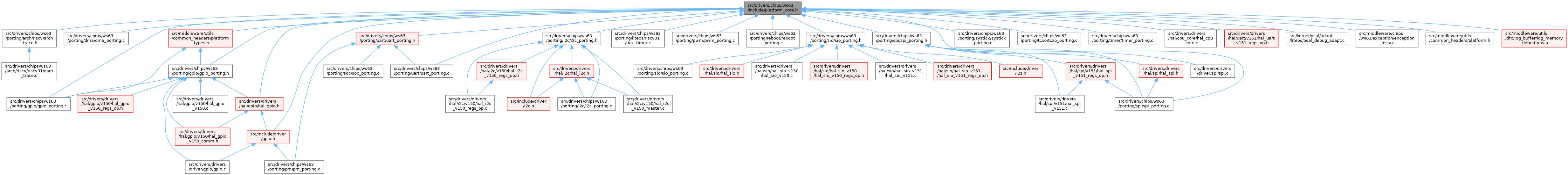

此图展示该文件直接或间接的被哪些文件引用了:

枚举 | |

| enum | qspi_bus_t { QSPI_BUS_0 = 0 , QSPI_BUS_1 , QSPI_BUS_NONE = 2 } |

| enum | uart_bus_t { UART_BUS_0 = 0 , UART_BUS_1 = 1 , UART_BUS_2 = 2 , UART_BUS_NONE = 3 } |

| UART bus. 更多... | |

| enum | i2c_bus_t { I2C_BUS_0 , I2C_BUS_1 , I2C_BUS_NONE = 2 } |

| I2C bus. 更多... | |

| enum | spi_bus_t { SPI_BUS_0 = 0 , SPI_BUS_1 , SPI_BUS_2 , SPI_BUS_3 , SPI_BUS_4 , SPI_BUS_5 , SPI_BUS_6 , SPI_BUS_NONE = 2 } |

| Definition of SPI bus index. 更多... | |

| enum | sio_bus_t { SIO_BUS_0 , SIO_NONE = 1 } |

| SIO(I2S/PCM) Bus. 更多... | |

| enum | slave_cpu_t { SLAVE_CPU_BT , SLAVE_CPU_MAX_NUM } |

函数 | |

| unsigned int | get_hso_buff (void) |