载入中...

搜索中...

未找到

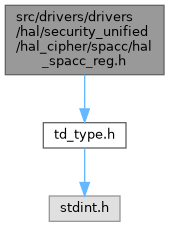

#include "td_type.h"

hal_spacc_reg.h 的引用(Include)关系图:

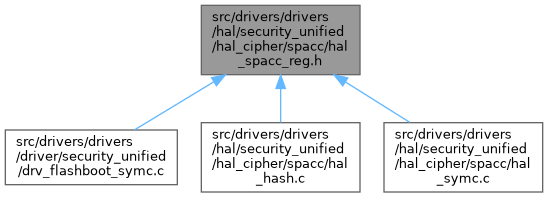

此图展示该文件直接或间接的被哪些文件引用了:

宏定义 | |

| #define | SPACC_CALC_CRG_CFG (0x8030) |

| #define | SPACC_IE (0x00000004) |

| #define | CHN_WHO_USED_CLR(used, chn) (used) &= ~(0x0fU << ((chn) * 4U)) |

| #define | CHN_WHO_USED_SET(used, chn, who) (used) |= (td_u32)(who) << ((td_u32)(chn) * 4U) |

| #define | CHN_WHO_USED_GET(used, chn) ((((used) >> ((chn) * 4U))) & 0x0fU) |

| #define | SPACC_HASH_CHN_LOCK 0x0040 |

| #define | SPACC_HASH_CHN_CLEAR_REQ 0x0068 |

| #define | SPACC_INT_RAW_HASH_CLEAR_FINISH 0x0014 |

| #define | CHANN_HASH_STATE_VAL_ADDR(id) (0xa004 + (id) * 0x80) |

| #define | CHANN_HASH_STATE_VAL(id) (0xa000 + (id) * 0x80) |

| #define | IN_HASH_CHN_CTRL(id) (0x5100 + ((id) - 1) * 0x100) |

| #define | IN_HASH_CHN_KEY_CTRL(id) (0x5110 + ((id) - 1) * 0x100) |

| #define | IN_HASH_CHN_NODE_START_ADDR_H(id) (0x5120 + ((id) - 1) * 0x100) |

| #define | IN_HASH_CHN_NODE_START_ADDR_L(id) (0x5124 + ((id) - 1) * 0x100) |

| #define | IN_HASH_CHN_NODE_LENGTH(id) (0x512c + ((id) - 1) * 0x100) |

| #define | IN_HASH_CHN_NODE_WR_POINT(id) (0x5130 + ((id) - 1) * 0x100) |

| #define | IN_HASH_CHN_NODE_RD_POINT(id) (0x5134 + ((id) - 1) * 0x100) |

| #define | IN_HASH_CHN_DATA_LEN(id) (0x51C0 + ((id) - 1) * 0x100) |

| #define | HASH_CHANN_RAW_INT 0x8600 |

| #define | HASH_CHANN_RAW_INT_EN 0x8604 |

| #define | TEE_HASH_CALC_CTRL_CHECK_ERR 0x8068 |

| #define | TEE_HASH_CALC_CTRL_CHECK_ERR_STATUS 0x806c |

| #define | REE_HASH_CALC_CTRL_CHECK_ERR 0x8078 |

| #define | REE_HASH_CALC_CTRL_CHECK_ERR_STATUS 0x807c |

| #define | PCPU_HASH_CALC_CTRL_CHECK_ERR 0x8088 |

| #define | PCPU_HASH_CALC_CTRL_CHECK_ERR_STATUS 0x808c |

| #define | AIDSP_HASH_CALC_CTRL_CHECK_ERR 0x8098 |

| #define | AIDSP_HASH_CALC_CTRL_CHECK_ERR_STATUS 0x809c |

| #define | ENCRYPT 0x5A |

| #define | DECRYPT 0xA5 |

| #define | SPACC_SYM_CHN_LOCK 0x0020 |

| #define | SPACC_INT_RAW_SYM_CLEAR_FINISH 0x0008 |

| #define | SPACC_EN_INT_RAW_SYM_CLEAR_FINISH 0x000c |

| #define | SPACC_SYM_CHN_CLEAR_REQ 0x0060 |

| #define | SPACC_BUS_ERR 0x0200 |

| #define | IN_SYM_CHN_CTRL(id) (0x4100 + ((id) - 1) * 0x100) |

| #define | IN_SYM_OUT_CTRL(id) (0x4104 + ((id) - 1) * 0x100) |

| #define | IN_SYM_CHN_KEY_CTRL(id) (0x4110 + ((id) - 1) * 0x100) |

| #define | IN_SYM_CHN_NODE_START_ADDR_H(id) (0x4120 + ((id) - 1) * 0x100) |

| #define | IN_SYM_CHN_NODE_START_ADDR_L(id) (0x4124 + ((id) - 1) * 0x100) |

| #define | IN_SYM_CHN_NODE_LENGTH(id) (0x412c + ((id) - 1) * 0x100) |

| #define | IN_SYM_CHN_NODE_WR_POINT(id) (0x4130 + ((id) - 1) * 0x100) |

| #define | IN_SYM_CHN_NODE_RD_POINT(id) (0x4134 + ((id) - 1) * 0x100) |

| #define | IN_SYM_CHN_NODE_CTRL(id) (0x4140 + ((id) - 1) * 0x100) |

| #define | DBG_IN_SYM_CHN_RD_ADDR_H(id) (0x41a0 + ((id) - 1) * 0x100) |

| #define | DBG_IN_SYM_CHN_RD_ADDR_L(id) (0x41a4 + ((id) - 1) * 0x100) |

| #define | DBG_IN_SYM_CHN_DATA_LEN(id) (0x41c0 + ((id) - 1) * 0x100) |

| #define | TEE_SYM_CALC_CTRL_CHECK_ERR 0x8060 |

| #define | TEE_SYM_CALC_CTRL_CHECK_ERR_STATUS 0x8064 |

| #define | REE_SYM_CALC_CTRL_CHECK_ERR 0x8070 |

| #define | REE_SYM_CALC_CTRL_CHECK_ERR_STATUS 0x8074 |

| #define | PCPU_SYM_CALC_CTRL_CHECK_ERR 0x8080 |

| #define | PCPU_SYM_CALC_CTRL_CHECK_ERR_STATUS 0x8084 |

| #define | AIDSP_SYM_CALC_CTRL_CHECK_ERR 0x8090 |

| #define | AIDSP_SYM_CALC_CTRL_CHECK_ERR_STATUS 0x8094 |

| #define | SYM_CHANN_RAW_INT 0x8610 |

| #define | SYM_CHANN_RAW_INT_EN 0x8614 |

| #define | SYM_CHANN_INT 0x8618 |

| #define | CHANN_CIPHER_IVOUT(id) (0x9000 + (id) * 0x80) |

| #define | CHANN_CIPHER_DFA_EN(id) (0x9020 + (id) * 0x80) |

| #define | OUT_SYM_CHAN_RAW_LAST_NODE_INT 0xc000 |

| #define | OUT_SYM_CHAN_RAW_LAST_NODE_INT_EN 0xc004 |

| #define | OUT_SYM_CHAN_LAST_NODE_INT 0xc008 |

| #define | OUT_SYM_CHAN_RAW_LEVEL_INT 0xc010 |

| #define | OUT_SYM_CHAN_RAW_LEVEL_INT_EN 0xc014 |

| #define | OUT_SYM_CHAN_LEVEL_INT 0xc018 |

| #define | OUT_SYM_CHN_STATUS(id) (0xD004 + ((id) - 1) * 0x100) |

| #define | OUT_SYM_CHN_NODE_START_ADDR_H(id) (0xD020 + ((id) - 1) * 0x100) |

| #define | OUT_SYM_CHN_NODE_START_ADDR_L(id) (0xD024 + ((id) - 1) * 0x100) |

| #define | OUT_SYM_CHN_NODE_LENGTH(id) (0xD028 + ((id) - 1) * 0x100) |

| #define | OUT_SYM_CHN_NODE_WR_POINT(id) (0xD030 + ((id) - 1) * 0x100) |

| #define | OUT_SYM_CHN_NODE_RD_POINT(id) (0xD034 + ((id) - 1) * 0x100) |

| #define | OUT_SYM_CHN_NODE_CTRL(id) (0xD040 + ((id) - 1) * 0x100) |

| #define | DBG_OUT_SYM_CHN_RD_ADDR_H(id) (0xD0a0 + ((id) - 1) * 0x100) |

| #define | DBG_OUT_SYM_CHN_RD_ADDR_L(id) (0xD0a4 + ((id) - 1) * 0x100) |

| #define | DBG_OUT_SYM_CHN_NODE_LEFT_BUF_LEN(id) (0xD0a8 + ((id) - 1) * 0x100) |

| #define | IN_SYM_CHN0_CTRL 0x4000 |

| #define | IN_SYM_CHN0_SPECIAL_CTRL 0x4004 |

| #define | IN_SYM_CHN0_KEY_CTRL 0x4010 |

| #define | IN_SYM_CHN0_IV_DATA_CTRL 0x4030 |

| #define | IN_SYM_CHN0_IV0 0x4040 |

| #define | IN_SYM_CHN0_IV1 0x4044 |

| #define | IN_SYM_CHN0_IV2 0x4048 |

| #define | IN_SYM_CHN0_IV3 0x404C |

| #define | IN_SYM_CHN0_DATA0 0x4050 |

| #define | IN_SYM_CHN0_DATA1 0x4054 |

| #define | IN_SYM_CHN0_DATA2 0x4058 |

| #define | IN_SYM_CHN0_DATA3 0x405C |

| #define | CHAN0_CIPHER_DOUT0 0x8100 |

| #define | SYMC_KEY_SIZE (32) |

| #define | NODE_DEPTH (2) |

| #define | SYMC_CFG_SECURE (0x05) |

| #define | SYMC_CFG_NON_SECURE (0x0A) |

| #define | ALG_DMA_REG (0) |

| #define | ALG_AES_REG (2) |

| #define | ALG_LEA_REG (4) |

| #define | ALG_SM4_REG (5) |

| #define | ALG_GHASH_REG (6) |

| #define | ALG_TDES_REG (7) |

| #define | MODE_ECB_REG (0x01) |

| #define | MODE_CBC_REG (0x03) |

| #define | MODE_CTR_REG (0x06) |

| #define | MODE_OFB_REG (0x07) |

| #define | MODE_CFB_REG (0x08) |

| #define | MODE_CCM_REG (0x09) |

| #define | MODE_GCM_REG (0x0A) |

| #define | MODE_GCTR_REG (0x0B) |

| #define | MODE_CMAC_REG (0x0C) |

| #define | MODE_CBC_NOOUT_REG (0x0D) |

| #define | MODE_GCTR_NOOUT_REG (0x0E) |

| #define | BIT_WIDTH_1_REG (2) |

| #define | BIT_WIDTH_8_REG (1) |

| #define | BIT_WIDTH_64_REG (3) |

| #define | BIT_WIDTH_128_REG (3) |

| #define | SYMC_IV_STATE_START (0) |

| #define | SYMC_IV_STATE_UPDATE (1) |

| #define | SYMC_IV_STATE_FINISH (2) |

枚举 | |

| enum | spacc_cpu_mask { SPACC_CPU_IDLE = 0x00000000 , SPACC_CPU_REE = 0x00000001 , SPACC_CPU_TEE = 0x00000002 , SPACC_CPU_PCPU = 0x00000004 , SPACC_CPU_AIDSP = 0x00000005 , SPACC_CPU_INVALID = 0xffffffff } |

宏定义说明

◆ AIDSP_HASH_CALC_CTRL_CHECK_ERR

| #define AIDSP_HASH_CALC_CTRL_CHECK_ERR 0x8098 |

◆ AIDSP_HASH_CALC_CTRL_CHECK_ERR_STATUS

| #define AIDSP_HASH_CALC_CTRL_CHECK_ERR_STATUS 0x809c |

◆ AIDSP_SYM_CALC_CTRL_CHECK_ERR

| #define AIDSP_SYM_CALC_CTRL_CHECK_ERR 0x8090 |

◆ AIDSP_SYM_CALC_CTRL_CHECK_ERR_STATUS

| #define AIDSP_SYM_CALC_CTRL_CHECK_ERR_STATUS 0x8094 |

◆ ALG_AES_REG

| #define ALG_AES_REG (2) |

◆ ALG_DMA_REG

| #define ALG_DMA_REG (0) |

◆ ALG_GHASH_REG

| #define ALG_GHASH_REG (6) |

◆ ALG_LEA_REG

| #define ALG_LEA_REG (4) |

◆ ALG_SM4_REG

| #define ALG_SM4_REG (5) |

◆ ALG_TDES_REG

| #define ALG_TDES_REG (7) |

◆ BIT_WIDTH_128_REG

| #define BIT_WIDTH_128_REG (3) |

◆ BIT_WIDTH_1_REG

| #define BIT_WIDTH_1_REG (2) |

◆ BIT_WIDTH_64_REG

| #define BIT_WIDTH_64_REG (3) |

◆ BIT_WIDTH_8_REG

| #define BIT_WIDTH_8_REG (1) |

◆ CHAN0_CIPHER_DOUT0

| #define CHAN0_CIPHER_DOUT0 0x8100 |

◆ CHANN_CIPHER_DFA_EN

| #define CHANN_CIPHER_DFA_EN | ( | id | ) | (0x9020 + (id) * 0x80) |

◆ CHANN_CIPHER_IVOUT

| #define CHANN_CIPHER_IVOUT | ( | id | ) | (0x9000 + (id) * 0x80) |

◆ CHANN_HASH_STATE_VAL

| #define CHANN_HASH_STATE_VAL | ( | id | ) | (0xa000 + (id) * 0x80) |

◆ CHANN_HASH_STATE_VAL_ADDR

| #define CHANN_HASH_STATE_VAL_ADDR | ( | id | ) | (0xa004 + (id) * 0x80) |

◆ CHN_WHO_USED_CLR

◆ CHN_WHO_USED_GET

◆ CHN_WHO_USED_SET

◆ DBG_IN_SYM_CHN_DATA_LEN

| #define DBG_IN_SYM_CHN_DATA_LEN | ( | id | ) | (0x41c0 + ((id) - 1) * 0x100) |

◆ DBG_IN_SYM_CHN_RD_ADDR_H

| #define DBG_IN_SYM_CHN_RD_ADDR_H | ( | id | ) | (0x41a0 + ((id) - 1) * 0x100) |

◆ DBG_IN_SYM_CHN_RD_ADDR_L

| #define DBG_IN_SYM_CHN_RD_ADDR_L | ( | id | ) | (0x41a4 + ((id) - 1) * 0x100) |

◆ DBG_OUT_SYM_CHN_NODE_LEFT_BUF_LEN

| #define DBG_OUT_SYM_CHN_NODE_LEFT_BUF_LEN | ( | id | ) | (0xD0a8 + ((id) - 1) * 0x100) |

◆ DBG_OUT_SYM_CHN_RD_ADDR_H

| #define DBG_OUT_SYM_CHN_RD_ADDR_H | ( | id | ) | (0xD0a0 + ((id) - 1) * 0x100) |

◆ DBG_OUT_SYM_CHN_RD_ADDR_L

| #define DBG_OUT_SYM_CHN_RD_ADDR_L | ( | id | ) | (0xD0a4 + ((id) - 1) * 0x100) |

◆ DECRYPT

| #define DECRYPT 0xA5 |

◆ ENCRYPT

| #define ENCRYPT 0x5A |

◆ HASH_CHANN_RAW_INT

| #define HASH_CHANN_RAW_INT 0x8600 |

◆ HASH_CHANN_RAW_INT_EN

| #define HASH_CHANN_RAW_INT_EN 0x8604 |

◆ IN_HASH_CHN_CTRL

| #define IN_HASH_CHN_CTRL | ( | id | ) | (0x5100 + ((id) - 1) * 0x100) |

◆ IN_HASH_CHN_DATA_LEN

| #define IN_HASH_CHN_DATA_LEN | ( | id | ) | (0x51C0 + ((id) - 1) * 0x100) |

◆ IN_HASH_CHN_KEY_CTRL

| #define IN_HASH_CHN_KEY_CTRL | ( | id | ) | (0x5110 + ((id) - 1) * 0x100) |

◆ IN_HASH_CHN_NODE_LENGTH

| #define IN_HASH_CHN_NODE_LENGTH | ( | id | ) | (0x512c + ((id) - 1) * 0x100) |

◆ IN_HASH_CHN_NODE_RD_POINT

| #define IN_HASH_CHN_NODE_RD_POINT | ( | id | ) | (0x5134 + ((id) - 1) * 0x100) |

◆ IN_HASH_CHN_NODE_START_ADDR_H

| #define IN_HASH_CHN_NODE_START_ADDR_H | ( | id | ) | (0x5120 + ((id) - 1) * 0x100) |

◆ IN_HASH_CHN_NODE_START_ADDR_L

| #define IN_HASH_CHN_NODE_START_ADDR_L | ( | id | ) | (0x5124 + ((id) - 1) * 0x100) |

◆ IN_HASH_CHN_NODE_WR_POINT

| #define IN_HASH_CHN_NODE_WR_POINT | ( | id | ) | (0x5130 + ((id) - 1) * 0x100) |

◆ IN_SYM_CHN0_CTRL

| #define IN_SYM_CHN0_CTRL 0x4000 |

◆ IN_SYM_CHN0_DATA0

| #define IN_SYM_CHN0_DATA0 0x4050 |

◆ IN_SYM_CHN0_DATA1

| #define IN_SYM_CHN0_DATA1 0x4054 |

◆ IN_SYM_CHN0_DATA2

| #define IN_SYM_CHN0_DATA2 0x4058 |

◆ IN_SYM_CHN0_DATA3

| #define IN_SYM_CHN0_DATA3 0x405C |

◆ IN_SYM_CHN0_IV0

| #define IN_SYM_CHN0_IV0 0x4040 |

◆ IN_SYM_CHN0_IV1

| #define IN_SYM_CHN0_IV1 0x4044 |

◆ IN_SYM_CHN0_IV2

| #define IN_SYM_CHN0_IV2 0x4048 |

◆ IN_SYM_CHN0_IV3

| #define IN_SYM_CHN0_IV3 0x404C |

◆ IN_SYM_CHN0_IV_DATA_CTRL

| #define IN_SYM_CHN0_IV_DATA_CTRL 0x4030 |

◆ IN_SYM_CHN0_KEY_CTRL

| #define IN_SYM_CHN0_KEY_CTRL 0x4010 |

◆ IN_SYM_CHN0_SPECIAL_CTRL

| #define IN_SYM_CHN0_SPECIAL_CTRL 0x4004 |

◆ IN_SYM_CHN_CTRL

| #define IN_SYM_CHN_CTRL | ( | id | ) | (0x4100 + ((id) - 1) * 0x100) |

◆ IN_SYM_CHN_KEY_CTRL

| #define IN_SYM_CHN_KEY_CTRL | ( | id | ) | (0x4110 + ((id) - 1) * 0x100) |

◆ IN_SYM_CHN_NODE_CTRL

| #define IN_SYM_CHN_NODE_CTRL | ( | id | ) | (0x4140 + ((id) - 1) * 0x100) |

◆ IN_SYM_CHN_NODE_LENGTH

| #define IN_SYM_CHN_NODE_LENGTH | ( | id | ) | (0x412c + ((id) - 1) * 0x100) |

◆ IN_SYM_CHN_NODE_RD_POINT

| #define IN_SYM_CHN_NODE_RD_POINT | ( | id | ) | (0x4134 + ((id) - 1) * 0x100) |

◆ IN_SYM_CHN_NODE_START_ADDR_H

| #define IN_SYM_CHN_NODE_START_ADDR_H | ( | id | ) | (0x4120 + ((id) - 1) * 0x100) |

◆ IN_SYM_CHN_NODE_START_ADDR_L

| #define IN_SYM_CHN_NODE_START_ADDR_L | ( | id | ) | (0x4124 + ((id) - 1) * 0x100) |

◆ IN_SYM_CHN_NODE_WR_POINT

| #define IN_SYM_CHN_NODE_WR_POINT | ( | id | ) | (0x4130 + ((id) - 1) * 0x100) |

◆ IN_SYM_OUT_CTRL

| #define IN_SYM_OUT_CTRL | ( | id | ) | (0x4104 + ((id) - 1) * 0x100) |

◆ MODE_CBC_NOOUT_REG

| #define MODE_CBC_NOOUT_REG (0x0D) |

◆ MODE_CBC_REG

| #define MODE_CBC_REG (0x03) |

◆ MODE_CCM_REG

| #define MODE_CCM_REG (0x09) |

◆ MODE_CFB_REG

| #define MODE_CFB_REG (0x08) |

◆ MODE_CMAC_REG

| #define MODE_CMAC_REG (0x0C) |

◆ MODE_CTR_REG

| #define MODE_CTR_REG (0x06) |

◆ MODE_ECB_REG

| #define MODE_ECB_REG (0x01) |

◆ MODE_GCM_REG

| #define MODE_GCM_REG (0x0A) |

◆ MODE_GCTR_NOOUT_REG

| #define MODE_GCTR_NOOUT_REG (0x0E) |

◆ MODE_GCTR_REG

| #define MODE_GCTR_REG (0x0B) |

◆ MODE_OFB_REG

| #define MODE_OFB_REG (0x07) |

◆ NODE_DEPTH

| #define NODE_DEPTH (2) |

◆ OUT_SYM_CHAN_LAST_NODE_INT

| #define OUT_SYM_CHAN_LAST_NODE_INT 0xc008 |

◆ OUT_SYM_CHAN_LEVEL_INT

| #define OUT_SYM_CHAN_LEVEL_INT 0xc018 |

◆ OUT_SYM_CHAN_RAW_LAST_NODE_INT

| #define OUT_SYM_CHAN_RAW_LAST_NODE_INT 0xc000 |

◆ OUT_SYM_CHAN_RAW_LAST_NODE_INT_EN

| #define OUT_SYM_CHAN_RAW_LAST_NODE_INT_EN 0xc004 |

◆ OUT_SYM_CHAN_RAW_LEVEL_INT

| #define OUT_SYM_CHAN_RAW_LEVEL_INT 0xc010 |

◆ OUT_SYM_CHAN_RAW_LEVEL_INT_EN

| #define OUT_SYM_CHAN_RAW_LEVEL_INT_EN 0xc014 |

◆ OUT_SYM_CHN_NODE_CTRL

| #define OUT_SYM_CHN_NODE_CTRL | ( | id | ) | (0xD040 + ((id) - 1) * 0x100) |

◆ OUT_SYM_CHN_NODE_LENGTH

| #define OUT_SYM_CHN_NODE_LENGTH | ( | id | ) | (0xD028 + ((id) - 1) * 0x100) |

◆ OUT_SYM_CHN_NODE_RD_POINT

| #define OUT_SYM_CHN_NODE_RD_POINT | ( | id | ) | (0xD034 + ((id) - 1) * 0x100) |

◆ OUT_SYM_CHN_NODE_START_ADDR_H

| #define OUT_SYM_CHN_NODE_START_ADDR_H | ( | id | ) | (0xD020 + ((id) - 1) * 0x100) |

◆ OUT_SYM_CHN_NODE_START_ADDR_L

| #define OUT_SYM_CHN_NODE_START_ADDR_L | ( | id | ) | (0xD024 + ((id) - 1) * 0x100) |

◆ OUT_SYM_CHN_NODE_WR_POINT

| #define OUT_SYM_CHN_NODE_WR_POINT | ( | id | ) | (0xD030 + ((id) - 1) * 0x100) |

◆ OUT_SYM_CHN_STATUS

| #define OUT_SYM_CHN_STATUS | ( | id | ) | (0xD004 + ((id) - 1) * 0x100) |

◆ PCPU_HASH_CALC_CTRL_CHECK_ERR

| #define PCPU_HASH_CALC_CTRL_CHECK_ERR 0x8088 |

◆ PCPU_HASH_CALC_CTRL_CHECK_ERR_STATUS

| #define PCPU_HASH_CALC_CTRL_CHECK_ERR_STATUS 0x808c |

◆ PCPU_SYM_CALC_CTRL_CHECK_ERR

| #define PCPU_SYM_CALC_CTRL_CHECK_ERR 0x8080 |

◆ PCPU_SYM_CALC_CTRL_CHECK_ERR_STATUS

| #define PCPU_SYM_CALC_CTRL_CHECK_ERR_STATUS 0x8084 |

◆ REE_HASH_CALC_CTRL_CHECK_ERR

| #define REE_HASH_CALC_CTRL_CHECK_ERR 0x8078 |

◆ REE_HASH_CALC_CTRL_CHECK_ERR_STATUS

| #define REE_HASH_CALC_CTRL_CHECK_ERR_STATUS 0x807c |

◆ REE_SYM_CALC_CTRL_CHECK_ERR

| #define REE_SYM_CALC_CTRL_CHECK_ERR 0x8070 |

◆ REE_SYM_CALC_CTRL_CHECK_ERR_STATUS

| #define REE_SYM_CALC_CTRL_CHECK_ERR_STATUS 0x8074 |

◆ SPACC_BUS_ERR

| #define SPACC_BUS_ERR 0x0200 |

◆ SPACC_CALC_CRG_CFG

| #define SPACC_CALC_CRG_CFG (0x8030) |

◆ SPACC_EN_INT_RAW_SYM_CLEAR_FINISH

| #define SPACC_EN_INT_RAW_SYM_CLEAR_FINISH 0x000c |

◆ SPACC_HASH_CHN_CLEAR_REQ

| #define SPACC_HASH_CHN_CLEAR_REQ 0x0068 |

◆ SPACC_HASH_CHN_LOCK

| #define SPACC_HASH_CHN_LOCK 0x0040 |

\Define the offset of HASH reg

◆ SPACC_IE

| #define SPACC_IE (0x00000004) |

◆ SPACC_INT_RAW_HASH_CLEAR_FINISH

| #define SPACC_INT_RAW_HASH_CLEAR_FINISH 0x0014 |

◆ SPACC_INT_RAW_SYM_CLEAR_FINISH

| #define SPACC_INT_RAW_SYM_CLEAR_FINISH 0x0008 |

◆ SPACC_SYM_CHN_CLEAR_REQ

| #define SPACC_SYM_CHN_CLEAR_REQ 0x0060 |

◆ SPACC_SYM_CHN_LOCK

| #define SPACC_SYM_CHN_LOCK 0x0020 |

◆ SYM_CHANN_INT

| #define SYM_CHANN_INT 0x8618 |

◆ SYM_CHANN_RAW_INT

| #define SYM_CHANN_RAW_INT 0x8610 |

◆ SYM_CHANN_RAW_INT_EN

| #define SYM_CHANN_RAW_INT_EN 0x8614 |

◆ SYMC_CFG_NON_SECURE

| #define SYMC_CFG_NON_SECURE (0x0A) |

◆ SYMC_CFG_SECURE

| #define SYMC_CFG_SECURE (0x05) |

◆ SYMC_IV_STATE_FINISH

| #define SYMC_IV_STATE_FINISH (2) |

◆ SYMC_IV_STATE_START

| #define SYMC_IV_STATE_START (0) |

◆ SYMC_IV_STATE_UPDATE

| #define SYMC_IV_STATE_UPDATE (1) |

◆ SYMC_KEY_SIZE

| #define SYMC_KEY_SIZE (32) |

◆ TEE_HASH_CALC_CTRL_CHECK_ERR

| #define TEE_HASH_CALC_CTRL_CHECK_ERR 0x8068 |

◆ TEE_HASH_CALC_CTRL_CHECK_ERR_STATUS

| #define TEE_HASH_CALC_CTRL_CHECK_ERR_STATUS 0x806c |

◆ TEE_SYM_CALC_CTRL_CHECK_ERR

| #define TEE_SYM_CALC_CTRL_CHECK_ERR 0x8060 |

◆ TEE_SYM_CALC_CTRL_CHECK_ERR_STATUS

| #define TEE_SYM_CALC_CTRL_CHECK_ERR_STATUS 0x8064 |

枚举类型说明

◆ spacc_cpu_mask

| enum spacc_cpu_mask |