载入中...

搜索中...

未找到

#include "common_def.h"#include "hal_sio_v151.h"#include "oal_interface.h"#include "soc_osal.h"#include "pinctrl_porting.h"#include "pinctrl.h"#include "chip_core_irq.h"#include "sio_porting.h"#include "debug_print.h"

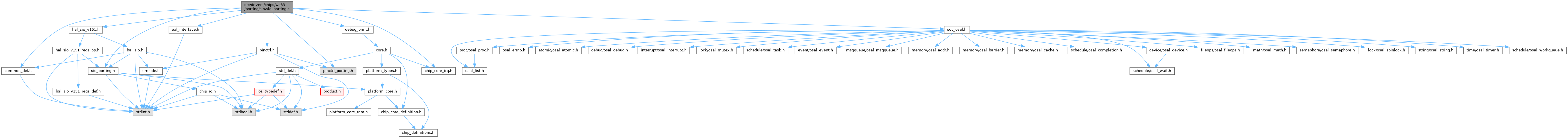

sio_porting.c 的引用(Include)关系图:

结构体 | |

| struct | sio_interrupt |

宏定义 | |

| #define | FREQ_OD_NEED 32 |

| #define | I2S_MCLK_DIV 2 |

| #define | I2S_MCLK_RATE 12288 |

| #define | I2S_BUS_0_REAL_BASE (I2S_BUS_0_BASE_ADDR - 0x3c) |

| #define | I2S_MERGE_TX_DATA_ADDR (I2S_BUS_0_REAL_BASE + 0xc0) |

| #define | I2S_MERGE_RX_DATA_ADDR (I2S_BUS_0_REAL_BASE + 0xa0) |

| #define | I2S_TX_SPLIT_LEFT_DATA_ADDR (I2S_BUS_0_REAL_BASE + 0x4c) |

| #define | I2S_TX_SPLIT_RIGHT_DATA_ADDR (I2S_BUS_0_REAL_BASE + 0x50) |

| #define | I2S_RX_SPLIT_LEFT_DATA_ADDR (I2S_BUS_0_REAL_BASE + 0x54) |

| #define | I2S_RX_SPLIT_RIGHT_DATA_ADDR (I2S_BUS_0_REAL_BASE + 0x58) |

| #define | HAL_I2S_CLK_CG_ADDR 0x44001100 |

| #define | CMU_NEW_CFG0 0x400034a0 |

| #define | HAL_I2S_CLK_CG_ON 0xffffffff |

| #define | I2S_CLKEN_BIT 12 |

| #define | I2S_BUS_CLKEN_BIT 11 |

| #define | CMU_DIV_AD_RSTN_SYNC_BIT 0 |

类型定义 | |

| typedef struct sio_interrupt | sio_interrupt_t |

宏定义说明

◆ CMU_DIV_AD_RSTN_SYNC_BIT

| #define CMU_DIV_AD_RSTN_SYNC_BIT 0 |

◆ CMU_NEW_CFG0

| #define CMU_NEW_CFG0 0x400034a0 |

◆ FREQ_OD_NEED

| #define FREQ_OD_NEED 32 |

Copyright (c) HiSilicon (Shanghai) Technologies Co., Ltd. 2023-2023. All rights reserved.

Description: Provides i2s port

History:

2023-03-10, Create file.

◆ HAL_I2S_CLK_CG_ADDR

| #define HAL_I2S_CLK_CG_ADDR 0x44001100 |

◆ HAL_I2S_CLK_CG_ON

| #define HAL_I2S_CLK_CG_ON 0xffffffff |

◆ I2S_BUS_0_REAL_BASE

| #define I2S_BUS_0_REAL_BASE (I2S_BUS_0_BASE_ADDR - 0x3c) |

◆ I2S_BUS_CLKEN_BIT

| #define I2S_BUS_CLKEN_BIT 11 |

◆ I2S_CLKEN_BIT

| #define I2S_CLKEN_BIT 12 |

◆ I2S_MCLK_DIV

| #define I2S_MCLK_DIV 2 |

◆ I2S_MCLK_RATE

| #define I2S_MCLK_RATE 12288 |

◆ I2S_MERGE_RX_DATA_ADDR

| #define I2S_MERGE_RX_DATA_ADDR (I2S_BUS_0_REAL_BASE + 0xa0) |

◆ I2S_MERGE_TX_DATA_ADDR

| #define I2S_MERGE_TX_DATA_ADDR (I2S_BUS_0_REAL_BASE + 0xc0) |

◆ I2S_RX_SPLIT_LEFT_DATA_ADDR

| #define I2S_RX_SPLIT_LEFT_DATA_ADDR (I2S_BUS_0_REAL_BASE + 0x54) |

◆ I2S_RX_SPLIT_RIGHT_DATA_ADDR

| #define I2S_RX_SPLIT_RIGHT_DATA_ADDR (I2S_BUS_0_REAL_BASE + 0x58) |

◆ I2S_TX_SPLIT_LEFT_DATA_ADDR

| #define I2S_TX_SPLIT_LEFT_DATA_ADDR (I2S_BUS_0_REAL_BASE + 0x4c) |

◆ I2S_TX_SPLIT_RIGHT_DATA_ADDR

| #define I2S_TX_SPLIT_RIGHT_DATA_ADDR (I2S_BUS_0_REAL_BASE + 0x50) |

类型定义说明

◆ sio_interrupt_t

| typedef struct sio_interrupt sio_interrupt_t |