载入中...

搜索中...

未找到

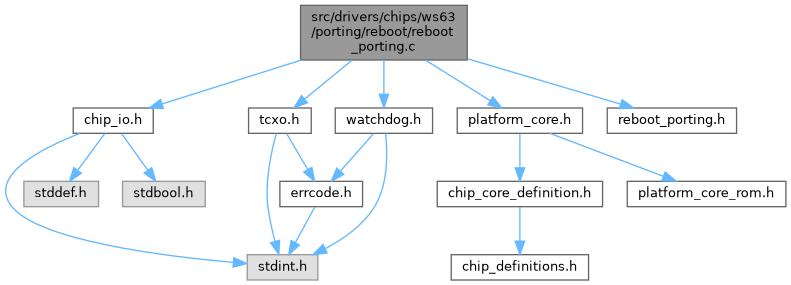

#include "chip_io.h"#include "tcxo.h"#include "watchdog.h"#include "platform_core.h"#include "reboot_porting.h"

reboot_porting.c 的引用(Include)关系图:

宏定义 | |

| #define | REG_SYS_RST_RECORD 0x40000098 |

| #define | SYS_HARD_RST (0x1 << 2) |

| #define | SYS_SOFT_RST (0x1 << 1) |

| #define | SYS_WDT_RST (0x1 << 0) |

| #define | GLB_CTL_RB 0x40000000 |

| #define | SYS_RST_RECORD_0 0x00A0 |

| #define | SYS_DIAG_CLR_1 0x00A4 |

| #define | SYS_WDT_RST_HIS 0x1 |

| #define | SYS_SOFT_RST_HIS 0x2 |

| #define | POR_RST_FILTER_HIS 0x8 |

函数 | |

| void | reboot_port_reboot_chip (void) |

| uint32_t | reboot_port_get_rst_reason (void) |

宏定义说明

◆ GLB_CTL_RB

| #define GLB_CTL_RB 0x40000000 |

◆ POR_RST_FILTER_HIS

| #define POR_RST_FILTER_HIS 0x8 |

◆ REG_SYS_RST_RECORD

| #define REG_SYS_RST_RECORD 0x40000098 |

Copyright (c) HiSilicon (Shanghai) Technologies Co., Ltd. 2022-2022. All rights reserved.

Description: Provides pwm port

History:

2022-09-16, Create file.

◆ SYS_DIAG_CLR_1

| #define SYS_DIAG_CLR_1 0x00A4 |

◆ SYS_HARD_RST

| #define SYS_HARD_RST (0x1 << 2) |

◆ SYS_RST_RECORD_0

| #define SYS_RST_RECORD_0 0x00A0 |

◆ SYS_SOFT_RST

| #define SYS_SOFT_RST (0x1 << 1) |

◆ SYS_SOFT_RST_HIS

| #define SYS_SOFT_RST_HIS 0x2 |

◆ SYS_WDT_RST

| #define SYS_WDT_RST (0x1 << 0) |

◆ SYS_WDT_RST_HIS

| #define SYS_WDT_RST_HIS 0x1 |