载入中...

搜索中...

未找到

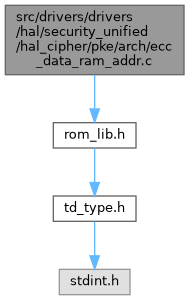

ecc_data_ram_addr.c 文件参考

#include "rom_lib.h"

ecc_data_ram_addr.c 的引用(Include)关系图:

变量说明

◆ ecc_addr_ax

| const td_u32 ecc_addr_ax = 12 |

◆ ecc_addr_ay

| const td_u32 ecc_addr_ay = 15 |

◆ ecc_addr_az

| const td_u32 ecc_addr_az = 18 |

◆ ecc_addr_const_0

| const td_u32 ecc_addr_const_0 = 78 |

◆ ecc_addr_const_1

| const td_u32 ecc_addr_const_1 = 75 |

◆ ecc_addr_cx

| const td_u32 ecc_addr_cx = 3 |

◆ ecc_addr_cy

| const td_u32 ecc_addr_cy = 6 |

◆ ecc_addr_cz

| const td_u32 ecc_addr_cz = 9 |

◆ ecc_addr_d

| const td_u32 ecc_addr_d = 15 |

◆ ecc_addr_e

| const td_u32 ecc_addr_e = 87 |

◆ ecc_addr_gx

| const td_u32 ecc_addr_gx = 27 |

◆ ecc_addr_gy

| const td_u32 ecc_addr_gy = 30 |

◆ ecc_addr_k

| const td_u32 ecc_addr_k = 12 |

◆ ecc_addr_m

| const td_u32 ecc_addr_m = 0 |

Copyright (c) HiSilicon (Shanghai) Technologies Co., Ltd. 2022-2022. All rights reserved. Description: define the data store address in the PKE DRAM.

Create: 2022-08-17

◆ ecc_addr_mont_1_n

| const td_u32 ecc_addr_mont_1_n = 72 |

◆ ecc_addr_mont_1_p

| const td_u32 ecc_addr_mont_1_p = 69 |

◆ ecc_addr_mont_a

| const td_u32 ecc_addr_mont_a = 63 |

◆ ecc_addr_mont_b

| const td_u32 ecc_addr_mont_b = 66 |

◆ ecc_addr_n

| const td_u32 ecc_addr_n = 57 |

◆ ecc_addr_p

| const td_u32 ecc_addr_p = 51 |

◆ ecc_addr_px

| const td_u32 ecc_addr_px = 21 |

◆ ecc_addr_py

| const td_u32 ecc_addr_py = 24 |

◆ ecc_addr_r

| const td_u32 ecc_addr_r = 84 |

◆ ecc_addr_rrn

| const td_u32 ecc_addr_rrn = 60 |

◆ ecc_addr_rrp

| const td_u32 ecc_addr_rrp = 54 |

◆ ecc_addr_rx

| const td_u32 ecc_addr_rx = 3 |

◆ ecc_addr_s

| const td_u32 ecc_addr_s = 81 |

◆ ecc_addr_t

| const td_u32 ecc_addr_t = 3 |

◆ ecc_addr_t0

| const td_u32 ecc_addr_t0 = 33 |

◆ ecc_addr_t1

| const td_u32 ecc_addr_t1 = 36 |

◆ ecc_addr_t2

| const td_u32 ecc_addr_t2 = 39 |

◆ ecc_addr_t3

| const td_u32 ecc_addr_t3 = 42 |

◆ ecc_addr_t4

| const td_u32 ecc_addr_t4 = 45 |

◆ ecc_addr_tp

| const td_u32 ecc_addr_tp = 48 |

◆ ecc_addr_u1

| const td_u32 ecc_addr_u1 = 3 |

◆ ecc_addr_u2

| const td_u32 ecc_addr_u2 = 6 |

◆ ecc_addr_v

| const td_u32 ecc_addr_v = 3 |