载入中...

搜索中...

未找到

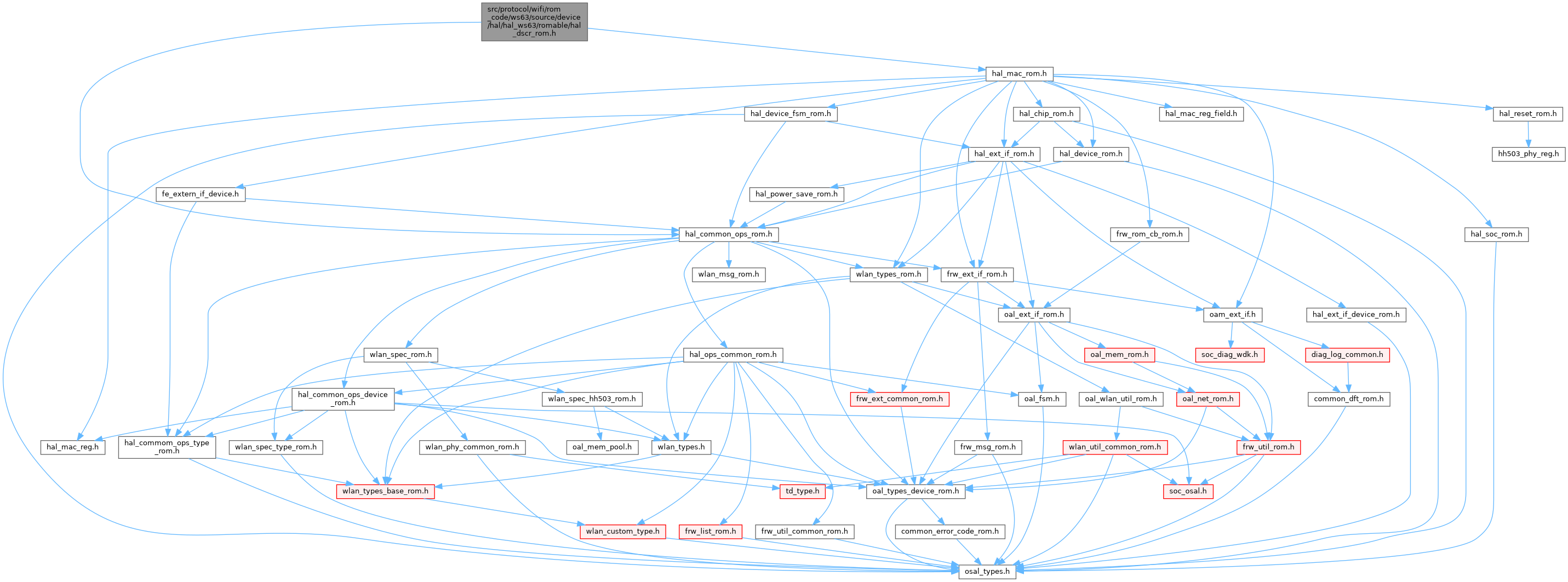

hal_dscr_rom.h 的引用(Include)关系图:

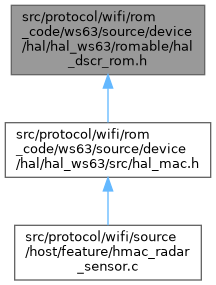

此图展示该文件直接或间接的被哪些文件引用了:

结构体 | |

| struct | hh503_tx_mac_mode_one_stru |

| struct | hh503_tx_mac_mode_two_stru |

| struct | hh503_tx_ctrl_desc_rate_tpc_stru |

| struct | hh503_tx_ctrl_dscr_one_stru |

| struct | tag_hh503_tx_ctrl_two_dscr_stru |

| struct | hh503_tx_ctrl_dscr_three_stru |

| struct | hh503_rx_buffer_addr_stru |

| union | rx_nss_rate_union |

| struct | hh503_rx_status_dscr_stru |

| struct | hh503_rx_debug_dscr_stru |

宏定义 | |

| #define | HH503_HW_RX_DSCR_LIST_ZERO 0 |

| #define | HAL_RX_MACHW_REG_TIMEOUT_COUNT 10 |

| #define | HAL_TX_DSCR_RATE_NUM 4 |

| #define | HAL_DSCR_BASE_ADDR 0xA |

| #define | HH503_MAC_BUS_MAX_2ADDR_OFFSET 20 |

类型定义 | |

| typedef struct tag_hh503_tx_ctrl_two_dscr_stru | hh503_tx_ctrl_dscr_two_stru |

| typedef osal_void(* | hh503_tx_wur_frame_set_dscr_cb) (hal_tx_dscr_stru *tx_dscr) |

| typedef osal_u32(* | hal_rx_record_frame_status_cb) (hal_to_dmac_device_stru *hal_device, osal_u32 *rx_dscr, hal_rx_dscr_queue_id_enum_uint8 queue_id) |

宏定义说明

◆ HAL_DSCR_BASE_ADDR

| #define HAL_DSCR_BASE_ADDR 0xA |

◆ HAL_RX_MACHW_REG_TIMEOUT_COUNT

| #define HAL_RX_MACHW_REG_TIMEOUT_COUNT 10 |

◆ HAL_TX_DSCR_RATE_NUM

| #define HAL_TX_DSCR_RATE_NUM 4 |

◆ HH503_HW_RX_DSCR_LIST_ZERO

| #define HH503_HW_RX_DSCR_LIST_ZERO 0 |

◆ HH503_MAC_BUS_MAX_2ADDR_OFFSET

| #define HH503_MAC_BUS_MAX_2ADDR_OFFSET 20 |

类型定义说明

◆ hal_rx_record_frame_status_cb

| typedef osal_u32(* hal_rx_record_frame_status_cb) (hal_to_dmac_device_stru *hal_device, osal_u32 *rx_dscr, hal_rx_dscr_queue_id_enum_uint8 queue_id) |

◆ hh503_tx_ctrl_dscr_two_stru

| typedef struct tag_hh503_tx_ctrl_two_dscr_stru hh503_tx_ctrl_dscr_two_stru |

◆ hh503_tx_wur_frame_set_dscr_cb

| typedef osal_void(* hh503_tx_wur_frame_set_dscr_cb) (hal_tx_dscr_stru *tx_dscr) |

函数说明

◆ hal_dump_all_tx_dscr()

| osal_void hal_dump_all_tx_dscr | ( | hal_to_dmac_device_stru * | hal_device, |

| osal_u32 | param | ||

| ) |

◆ hal_get_tx_dscr_field()

| osal_void hal_get_tx_dscr_field | ( | const hal_to_dmac_device_stru * | hal_device, |

| hal_tx_dscr_stru * | tx_dscr | ||

| ) |

◆ hal_get_tx_dscr_pn_lsb()

| osal_u32 hal_get_tx_dscr_pn_lsb | ( | hal_tx_dscr_stru * | tx_dscr | ) |

◆ hal_get_tx_dscr_pn_msb()

| osal_u32 hal_get_tx_dscr_pn_msb | ( | hal_tx_dscr_stru * | tx_dscr | ) |

◆ hal_get_tx_dscr_seq_num()

| osal_u32 hal_get_tx_dscr_seq_num | ( | hal_tx_dscr_stru * | tx_dscr | ) |

◆ hal_rx_add_dscr()

| osal_void hal_rx_add_dscr | ( | hal_to_dmac_device_stru * | hal_device, |

| hal_rx_dscr_queue_id_enum_uint8 | queue_num | ||

| ) |

◆ hal_set_tx_dscr_pn_lsb()

| osal_void hal_set_tx_dscr_pn_lsb | ( | hal_tx_dscr_stru * | tx_dscr, |

| osal_u32 | tx_pn_lsb | ||

| ) |

◆ hal_set_tx_dscr_pn_msb()

| osal_void hal_set_tx_dscr_pn_msb | ( | hal_tx_dscr_stru * | tx_dscr, |

| osal_u32 | tx_pn_msb | ||

| ) |

◆ hal_set_tx_dscr_seq_num()

| osal_void hal_set_tx_dscr_seq_num | ( | hal_tx_dscr_stru * | tx_dscr, |

| osal_u32 | seq_num_fld | ||

| ) |

◆ hal_tx_dscr_get_real_addr()

◆ hal_tx_dscr_get_sw_addr()

◆ hh503_get_real_addr()

◆ hh503_get_rx_dscr_addr()

◆ hh503_get_tx_dscr_addr()

| osal_void hh503_get_tx_dscr_addr | ( | hal_tx_dscr_stru ** | tx_dscr | ) |

◆ hh503_rx_alloc_netbuf_and_dscr()

| osal_u32 hh503_rx_alloc_netbuf_and_dscr | ( | hal_to_dmac_device_stru * | hal_device, |

| hal_rx_dscr_queue_id_enum_uint8 | queue_num | ||

| ) |

◆ hh503_rx_ctrl_dscr_link()

| osal_void hh503_rx_ctrl_dscr_link | ( | hal_rx_dscr_stru * | rx_dscr_prev, |

| hal_rx_dscr_stru * | rx_dscr | ||

| ) |

◆ hh503_rx_set_ctrl_dscr()

| osal_u32 hh503_rx_set_ctrl_dscr | ( | hal_rx_dscr_stru * | rx_dscr, |

| oal_dmac_netbuf_stru * | netbuf | ||

| ) |

◆ hh503_rx_set_status_dscr()

| osal_void hh503_rx_set_status_dscr | ( | hal_rx_dscr_stru * | rx_dscr, |

| hal_rx_status_enum_uint8 | status | ||

| ) |

◆ hh503_tx_wur_frame_set_dscr()

| osal_void hh503_tx_wur_frame_set_dscr | ( | hal_tx_dscr_stru * | tx_dscr | ) |