载入中...

搜索中...

未找到

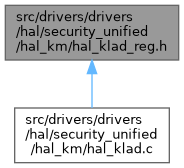

此图展示该文件直接或间接的被哪些文件引用了:

结构体 | |

| union | hkl_lock_ctrl |

| union | hkl_com_lock_info |

| union | hkl_com_lock_status |

| union | hkl_unlock_ctrl |

| union | kl_com_ctrl |

| union | kl_com_status |

| union | hkl_key_sec_cfg |

| union | hkl_key_addr |

| union | hkl_key_cfg |

| union | kl_clr_ctrl |

| union | hkl_nonce_ctrl |

| union | hkl_nonce_status |

| union | hkl_clr_lock_info |

| union | hkl_clr_lock_status |

| union | hkl_clr_ctrl |

| union | hkl_fp_lock_info |

| union | hkl_fp_lock_status |

| union | hkl_fp_rk_sel |

| union | hkl_fp_ctrl |

| union | hkl_fp_status |

| union | hkl_fp_dec_ctrl |

| union | hkl_ta_lock_info |

| union | hkl_ta_lock_status |

| union | hkl_ta_ctrl |

| union | hkl_ta_status |

| union | hkl_csgk2_lock_info |

| union | hkl_csgk2_lock_status |

| union | hkl_csgk2_ctrl |

| union | hkl_csgk2_disable |

| union | hkl_csgk2_disable_lock |

| union | hkl_alarm_info |

| union | sbrk_disable |

| union | abrk_disable |

| union | kl_int_cfg |

| union | kl_int_status |

| union | kl_int_raw |

宏定义说明

◆ ABRK_DISABLE

| #define ABRK_DISABLE (KLAD_REG_OFFSET + 0x064) |

◆ ABRK_DISABLE_VAL

| #define ABRK_DISABLE_VAL 0x5 |

◆ ATTACH_FLASH

| #define ATTACH_FLASH 2 |

◆ ATTACH_HMAC

| #define ATTACH_HMAC 4 |

◆ ATTACH_MCIPHER

| #define ATTACH_MCIPHER 3 |

◆ BYTE_TO_BITS

| #define BYTE_TO_BITS 8 |

◆ CLEAR_HMAC_KEY_BLOCK_SIZE_1024

| #define CLEAR_HMAC_KEY_BLOCK_SIZE_1024 128 |

◆ CLEAR_HMAC_KEY_BLOCK_SIZE_512

| #define CLEAR_HMAC_KEY_BLOCK_SIZE_512 64 |

◆ CLEAR_HMAC_KEY_CAL_CNT_1024

| #define CLEAR_HMAC_KEY_CAL_CNT_1024 8 |

◆ CLEAR_HMAC_KEY_CAL_CNT_512

| #define CLEAR_HMAC_KEY_CAL_CNT_512 4 |

◆ HKL_KEY_LEN

| #define HKL_KEY_LEN 16 |

◆ HKL_KEY_LEN_32

| #define HKL_KEY_LEN_32 32 |

◆ KALD_DATA_IN_REG_NUM

| #define KALD_DATA_IN_REG_NUM 4 |

◆ KC_ERROR

| #define KC_ERROR (KLAD_REG_OFFSET + 0x03c) |

◆ KDF_ABRK

| #define KDF_ABRK 6 |

◆ KDF_ABRK2

| #define KDF_ABRK2 17 |

◆ KDF_ABRK_REE

| #define KDF_ABRK_REE 20 |

◆ KDF_DFT_JTAG

| #define KDF_DFT_JTAG 0x15 |

◆ KDF_DRK

| #define KDF_DRK 13 |

◆ KDF_FDRK

| #define KDF_FDRK 11 |

◆ KDF_FUNC_JTAG

| #define KDF_FUNC_JTAG 0x13 |

◆ KDF_MDRK0

| #define KDF_MDRK0 10 |

◆ KDF_MDRK1

| #define KDF_MDRK1 12 |

◆ KDF_MDRK2

| #define KDF_MDRK2 14 |

◆ KDF_MDRK3

| #define KDF_MDRK3 15 |

◆ KDF_ODRK0

| #define KDF_ODRK0 7 |

◆ KDF_ODRK1

| #define KDF_ODRK1 8 |

◆ KDF_PSK

| #define KDF_PSK 18 |

◆ KDF_RDRK

| #define KDF_RDRK 9 |

◆ KDF_RDRK_REE

| #define KDF_RDRK_REE 22 |

◆ KDF_SBRK

| #define KDF_SBRK 5 |

◆ KDF_SBRK2

| #define KDF_SBRK2 16 |

◆ KDF_SW_GEN

| #define KDF_SW_GEN 3 |

◆ KDF_TEE_JTAG

| #define KDF_TEE_JTAG 0x14 |

◆ KDF_USD

| #define KDF_USD 4 |

◆ KEY_SIZE_128_BIT

| #define KEY_SIZE_128_BIT 16 |

◆ KEY_SIZE_128_BIT_REG_VAL

| #define KEY_SIZE_128_BIT_REG_VAL 0x1 |

◆ KEY_SIZE_192_BIT

| #define KEY_SIZE_192_BIT 24 |

◆ KEY_SIZE_192_BIT_REG_VAL

| #define KEY_SIZE_192_BIT_REG_VAL 0x2 |

◆ KEY_SIZE_256_BIT

| #define KEY_SIZE_256_BIT 32 |

◆ KEY_SIZE_256_BIT_REG_VAL

| #define KEY_SIZE_256_BIT_REG_VAL 0x3 |

◆ KEY_SIZE_64_BIT

| #define KEY_SIZE_64_BIT 8 |

Copyright (c) HiSilicon (Shanghai) Technologies Co., Ltd. 2023-2023. All rights reserved.

Description: hal klad register header.

History:

2023-03-22, Create file.

◆ KEY_SIZE_64_BIT_REG_VAL

| #define KEY_SIZE_64_BIT_REG_VAL 0x0 |

◆ KL_ALARM_INFO

| #define KL_ALARM_INFO (KLAD_REG_OFFSET + 0x600) |

◆ KL_CLR_CTRL

| #define KL_CLR_CTRL (KLAD_REG_OFFSET + 0x438) |

◆ KL_COM_CTRL

| #define KL_COM_CTRL (KLAD_REG_OFFSET + 0x084) |

◆ KL_COM_LOCK_INFO

| #define KL_COM_LOCK_INFO (KLAD_REG_OFFSET + 0x07c) |

◆ KL_COM_LOCK_STATUS

| #define KL_COM_LOCK_STATUS (KLAD_REG_OFFSET + 0x080) |

◆ KL_COM_STATUS

| #define KL_COM_STATUS (KLAD_REG_OFFSET + 0x088) |

◆ KL_CRC

| #define KL_CRC (KLAD_REG_OFFSET + 0x034) |

◆ KL_DATA_IN

| #define KL_DATA_IN | ( | n | ) | (KLAD_REG_OFFSET + 0x000 + ((n) * 0x4)) /* n 0~3 */ |

◆ KL_DATA_IN_0

| #define KL_DATA_IN_0 (KLAD_REG_OFFSET + 0x000) |

◆ KL_DATA_IN_1

| #define KL_DATA_IN_1 (KLAD_REG_OFFSET + 0x004) |

◆ KL_DATA_IN_2

| #define KL_DATA_IN_2 (KLAD_REG_OFFSET + 0x008) |

◆ KL_DATA_IN_3

| #define KL_DATA_IN_3 (KLAD_REG_OFFSET + 0x00c) |

◆ KL_ERROR

| #define KL_ERROR (KLAD_REG_OFFSET + 0x038) |

◆ KL_INT

| #define KL_INT (KLAD_REG_OFFSET + 0x048) |

◆ KL_INT_EN

| #define KL_INT_EN (KLAD_REG_OFFSET + 0x040) |

◆ KL_INT_RAW

| #define KL_INT_RAW (KLAD_REG_OFFSET + 0x044) |

◆ KL_KEY_ADDR

| #define KL_KEY_ADDR (KLAD_REG_OFFSET + 0x010) |

◆ KL_KEY_CFG

| #define KL_KEY_CFG (KLAD_REG_OFFSET + 0x014) |

◆ KL_KEY_SEC_CFG

| #define KL_KEY_SEC_CFG (KLAD_REG_OFFSET + 0x018) |

◆ KL_LOCK_CTRL

| #define KL_LOCK_CTRL (KLAD_REG_OFFSET + 0x074) |

◆ KL_RK_GEN_STATUS

| #define KL_RK_GEN_STATUS (KLAD_REG_OFFSET + 0x070) |

◆ KL_STATE

| #define KL_STATE (KLAD_REG_OFFSET + 0x030) |

◆ KL_UNLOCK_CTRL

| #define KL_UNLOCK_CTRL (KLAD_REG_OFFSET + 0x078) |

◆ KLAD_CHANNEL_MAX_SUPPORT

| #define KLAD_CHANNEL_MAX_SUPPORT 1 |

◆ KLAD_CLEAR_KEY_INVALID_HMAC

| #define KLAD_CLEAR_KEY_INVALID_HMAC 0xff |

◆ KLAD_DEST_TYPE_AI_AUDIO

| #define KLAD_DEST_TYPE_AI_AUDIO 4 |

◆ KLAD_DEST_TYPE_AI_NPU

| #define KLAD_DEST_TYPE_AI_NPU 5 |

◆ KLAD_DEST_TYPE_FLASH

| #define KLAD_DEST_TYPE_FLASH 7 |

◆ KLAD_DEST_TYPE_INVALID

| #define KLAD_DEST_TYPE_INVALID 0 |

◆ KLAD_DEST_TYPE_INVALID_KSLOT

| #define KLAD_DEST_TYPE_INVALID_KSLOT 0xffffffff |

◆ KLAD_DEST_TYPE_MCIPHER

| #define KLAD_DEST_TYPE_MCIPHER 1 |

◆ KLAD_INVALID_HANDLE_INDEX

| #define KLAD_INVALID_HANDLE_INDEX (-1) |

◆ KLAD_KEY_TYPE_ABRK0

| #define KLAD_KEY_TYPE_ABRK0 0x2 |

◆ KLAD_KEY_TYPE_ABRK1

| #define KLAD_KEY_TYPE_ABRK1 0x3 |

◆ KLAD_KEY_TYPE_ABRK2

| #define KLAD_KEY_TYPE_ABRK2 0x11 |

◆ KLAD_KEY_TYPE_ABRK_REE

| #define KLAD_KEY_TYPE_ABRK_REE 0x15 |

◆ KLAD_KEY_TYPE_DRK0

| #define KLAD_KEY_TYPE_DRK0 0xc |

◆ KLAD_KEY_TYPE_DRK1

| #define KLAD_KEY_TYPE_DRK1 0xd |

◆ KLAD_KEY_TYPE_FDRK0

| #define KLAD_KEY_TYPE_FDRK0 0x4 |

◆ KLAD_KEY_TYPE_MDRK0

| #define KLAD_KEY_TYPE_MDRK0 0x8 |

◆ KLAD_KEY_TYPE_OARK0

| #define KLAD_KEY_TYPE_OARK0 0x6 |

◆ KLAD_KEY_TYPE_ODRK0

| #define KLAD_KEY_TYPE_ODRK0 0x5 |

◆ KLAD_KEY_TYPE_ODRK1

| #define KLAD_KEY_TYPE_ODRK1 0x7 |

◆ KLAD_KEY_TYPE_PSK

| #define KLAD_KEY_TYPE_PSK 0x12 |

◆ KLAD_KEY_TYPE_RDRK0

| #define KLAD_KEY_TYPE_RDRK0 0xe |

◆ KLAD_KEY_TYPE_RDRK1

| #define KLAD_KEY_TYPE_RDRK1 0xf |

◆ KLAD_KEY_TYPE_RDRK_REE

| #define KLAD_KEY_TYPE_RDRK_REE 0x17 |

◆ KLAD_KEY_TYPE_SBRK0

| #define KLAD_KEY_TYPE_SBRK0 0x0 |

◆ KLAD_KEY_TYPE_SBRK1

| #define KLAD_KEY_TYPE_SBRK1 0x1 |

◆ KLAD_KEY_TYPE_SBRK2

| #define KLAD_KEY_TYPE_SBRK2 0x10 |

◆ KLAD_LOCK_REG_CONFIG_VALUE

| #define KLAD_LOCK_REG_CONFIG_VALUE 1 |

◆ KLAD_REG_OFFSET

| #define KLAD_REG_OFFSET (0x00001000) |

◆ KLAD_UNLOCK_REG_CONFIG_VALUE

| #define KLAD_UNLOCK_REG_CONFIG_VALUE 1 |

◆ KLAD_UNLOCK_STATUS

| #define KLAD_UNLOCK_STATUS 0x0 |

◆ SBRK_DISABLE

| #define SBRK_DISABLE (KLAD_REG_OFFSET + 0x060) |

◆ SBRK_DISABLE_VAL

| #define SBRK_DISABLE_VAL 0x5 |