载入中...

搜索中...

未找到

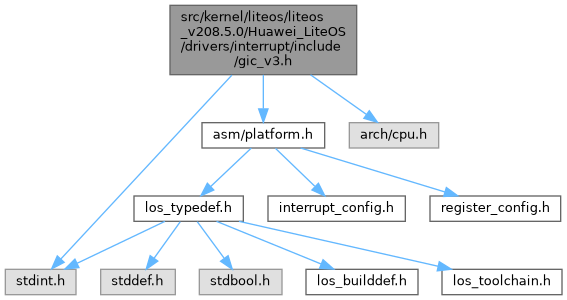

gic_v3.h 的引用(Include)关系图:

宏定义 | |

| #define | BIT_32(bit) (1u << bit) |

| #define | BIT_64(bit) (1ul << bit) |

| #define | ICC_CTLR_EL1 "c12, c12, 4" |

| #define | ICC_PMR_EL1 "c4, c6, 0" |

| #define | ICC_IAR1_EL1 "c12, c12, 0" |

| #define | ICC_SRE_EL1 "c12, c12, 5" |

| #define | ICC_BPR1_EL1 "c12, c12, 3" |

| #define | ICC_IGRPEN1_EL1 "c12, c12, 7" |

| #define | ICC_EOIR1_EL1 "c12, c12, 1" |

| #define | ICC_SGI1R_EL1 "c12" |

| #define | CTLR_ENALBE_G1 BIT_32(0) |

| #define | CTLR_ENABLE_G1A BIT_32(1) |

| #define | CTLR_ARE_NS BIT_32(4) |

| #define | GICD_CTLR_RWP BIT_32(31) |

| #define | GICD_CIDR0 (GICD_OFFSET + 0xfff0) |

| #define | GICD_CIDR1 (GICD_OFFSET + 0xfff4) |

| #define | GICD_CIDR2 (GICD_OFFSET + 0xfff8) |

| #define | GICD_CIDR3 (GICD_OFFSET + 0xfffc) |

| #define | GICD_PIDR0 (GICD_OFFSET + 0xffe0) |

| #define | GICD_PIDR1 (GICD_OFFSET + 0xffe4) |

| #define | GICD_PIDR2 (GICD_OFFSET + 0xffe8) |

| #define | GICD_PIDR3 (GICD_OFFSET + 0xffec) |

| #define | GICD_PIDR2_ARCHREV_SHIFT 4 |

| #define | GICD_PIDR2_ARCHREV_MASK 0xf |

| #define | GICR_SGI_OFFSET (GICR_OFFSET + 0x10000) |

| #define | GICR_CTLR(i) (GICR_OFFSET + GICR_STRIDE * (i) + 0x0000) |

| #define | GICR_IIDR(i) (GICR_OFFSET + GICR_STRIDE * (i) + 0x0004) |

| #define | GICR_TYPER(i) (GICR_OFFSET + GICR_STRIDE * (i) + 0x0008) |

| #define | GICR_STATUSR(i) (GICR_OFFSET + GICR_STRIDE * (i) + 0x0010) |

| #define | GICR_WAKER(i) (GICR_OFFSET + GICR_STRIDE * (i) + 0x0014) |

| #define | GICR_PWRR(i) (GICR_OFFSET + GICR_STRIDE * (i) + 0x0024) |

| #define | GICR_IGROUPR0(i) (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0080) |

| #define | GICR_IGRPMOD0(i) (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0d00) |

| #define | GICR_ISENABLER0(i) (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0100) |

| #define | GICR_ICENABLER0(i) (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0180) |

| #define | GICR_ISPENDR0(i) (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0200) |

| #define | GICR_ICPENDR0(i) (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0280) |

| #define | GICR_ISACTIVER0(i) (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0300) |

| #define | GICR_ICACTIVER0(i) (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0380) |

| #define | GICR_IPRIORITYR(i, n) (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0400 + (n) * 4) |

| #define | GICR_ICFGR0(i) (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0c00) |

| #define | GICR_ICFGR1(i) (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0c04) |

| #define | GICR_NSACR(i) (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0e00) |

| #define | GICR_WAKER_PROCESSORSLEEP_LEN 1U |

| #define | GICR_WAKER_PROCESSORSLEEP_OFFSET 1 |

| #define | GICR_WAKER_CHILDRENASLEEP_LEN 1U |

| #define | GICR_WAKER_CHILDRENASLEEP_OFFSET 2 |

| #define | GICR_WAKER_PROCESSORSLEEP (GICR_WAKER_PROCESSORSLEEP_LEN << GICR_WAKER_PROCESSORSLEEP_OFFSET) |

| #define | GICR_WAKER_CHILDRENASLEEP (GICR_WAKER_CHILDRENASLEEP_LEN << GICR_WAKER_CHILDRENASLEEP_OFFSET) |

| #define | GIC_LPI_CHECK_RETURN(intNum) |

| #define | GIC_PRIORITY_MASK 0xFFU |

| #define | GIC_PRIORITY_OFFSET 8U |

| #define | PRIORITY_SHIFT ((MAX_BINARY_POINT_VALUE + 1) % GIC_PRIORITY_OFFSET) |

函数 | |

| STATIC INLINE VOID | GiccSetCtlr (UINT32 val) |

| STATIC INLINE VOID | GiccSetPmr (UINT32 val) |

| STATIC INLINE VOID | GiccSetIgrpen1 (UINT32 val) |

| STATIC INLINE UINT32 | GiccGetSre (VOID) |

| STATIC INLINE VOID | GiccSetSre (UINT32 val) |

| STATIC INLINE VOID | GiccSetEoir (UINT32 val) |

| STATIC INLINE UINT32 | GiccGetIar (VOID) |

| STATIC INLINE VOID | GiccSetSgi1r (UINT64 val) |

| STATIC INLINE VOID | GiccSetBpr1 (UINT32 val) |

| STATIC INLINE UINT64 | MpidrToAffinity (UINT64 mpidr) |

宏定义说明

◆ BIT_32

◆ BIT_64

◆ CTLR_ARE_NS

| #define CTLR_ARE_NS BIT_32(4) |

◆ CTLR_ENABLE_G1A

| #define CTLR_ENABLE_G1A BIT_32(1) |

◆ CTLR_ENALBE_G1

| #define CTLR_ENALBE_G1 BIT_32(0) |

◆ GIC_LPI_CHECK_RETURN

| #define GIC_LPI_CHECK_RETURN | ( | intNum | ) |

◆ GIC_PRIORITY_MASK

| #define GIC_PRIORITY_MASK 0xFFU |

◆ GIC_PRIORITY_OFFSET

| #define GIC_PRIORITY_OFFSET 8U |

◆ GICD_CIDR0

| #define GICD_CIDR0 (GICD_OFFSET + 0xfff0) |

◆ GICD_CIDR1

| #define GICD_CIDR1 (GICD_OFFSET + 0xfff4) |

◆ GICD_CIDR2

| #define GICD_CIDR2 (GICD_OFFSET + 0xfff8) |

◆ GICD_CIDR3

| #define GICD_CIDR3 (GICD_OFFSET + 0xfffc) |

◆ GICD_CTLR_RWP

| #define GICD_CTLR_RWP BIT_32(31) |

◆ GICD_PIDR0

| #define GICD_PIDR0 (GICD_OFFSET + 0xffe0) |

◆ GICD_PIDR1

| #define GICD_PIDR1 (GICD_OFFSET + 0xffe4) |

◆ GICD_PIDR2

| #define GICD_PIDR2 (GICD_OFFSET + 0xffe8) |

◆ GICD_PIDR2_ARCHREV_MASK

| #define GICD_PIDR2_ARCHREV_MASK 0xf |

◆ GICD_PIDR2_ARCHREV_SHIFT

| #define GICD_PIDR2_ARCHREV_SHIFT 4 |

◆ GICD_PIDR3

| #define GICD_PIDR3 (GICD_OFFSET + 0xffec) |

◆ GICR_CTLR

| #define GICR_CTLR | ( | i | ) | (GICR_OFFSET + GICR_STRIDE * (i) + 0x0000) |

◆ GICR_ICACTIVER0

| #define GICR_ICACTIVER0 | ( | i | ) | (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0380) |

◆ GICR_ICENABLER0

| #define GICR_ICENABLER0 | ( | i | ) | (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0180) |

◆ GICR_ICFGR0

| #define GICR_ICFGR0 | ( | i | ) | (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0c00) |

◆ GICR_ICFGR1

| #define GICR_ICFGR1 | ( | i | ) | (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0c04) |

◆ GICR_ICPENDR0

| #define GICR_ICPENDR0 | ( | i | ) | (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0280) |

◆ GICR_IGROUPR0

| #define GICR_IGROUPR0 | ( | i | ) | (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0080) |

◆ GICR_IGRPMOD0

| #define GICR_IGRPMOD0 | ( | i | ) | (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0d00) |

◆ GICR_IIDR

| #define GICR_IIDR | ( | i | ) | (GICR_OFFSET + GICR_STRIDE * (i) + 0x0004) |

◆ GICR_IPRIORITYR

| #define GICR_IPRIORITYR | ( | i, | |

| n | |||

| ) | (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0400 + (n) * 4) |

◆ GICR_ISACTIVER0

| #define GICR_ISACTIVER0 | ( | i | ) | (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0300) |

◆ GICR_ISENABLER0

| #define GICR_ISENABLER0 | ( | i | ) | (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0100) |

◆ GICR_ISPENDR0

| #define GICR_ISPENDR0 | ( | i | ) | (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0200) |

◆ GICR_NSACR

| #define GICR_NSACR | ( | i | ) | (GICR_SGI_OFFSET + GICR_STRIDE * (i) + 0x0e00) |

◆ GICR_PWRR

| #define GICR_PWRR | ( | i | ) | (GICR_OFFSET + GICR_STRIDE * (i) + 0x0024) |

◆ GICR_SGI_OFFSET

| #define GICR_SGI_OFFSET (GICR_OFFSET + 0x10000) |

◆ GICR_STATUSR

| #define GICR_STATUSR | ( | i | ) | (GICR_OFFSET + GICR_STRIDE * (i) + 0x0010) |

◆ GICR_TYPER

| #define GICR_TYPER | ( | i | ) | (GICR_OFFSET + GICR_STRIDE * (i) + 0x0008) |

◆ GICR_WAKER

| #define GICR_WAKER | ( | i | ) | (GICR_OFFSET + GICR_STRIDE * (i) + 0x0014) |

◆ GICR_WAKER_CHILDRENASLEEP

| #define GICR_WAKER_CHILDRENASLEEP (GICR_WAKER_CHILDRENASLEEP_LEN << GICR_WAKER_CHILDRENASLEEP_OFFSET) |

◆ GICR_WAKER_CHILDRENASLEEP_LEN

| #define GICR_WAKER_CHILDRENASLEEP_LEN 1U |

◆ GICR_WAKER_CHILDRENASLEEP_OFFSET

| #define GICR_WAKER_CHILDRENASLEEP_OFFSET 2 |

◆ GICR_WAKER_PROCESSORSLEEP

| #define GICR_WAKER_PROCESSORSLEEP (GICR_WAKER_PROCESSORSLEEP_LEN << GICR_WAKER_PROCESSORSLEEP_OFFSET) |

◆ GICR_WAKER_PROCESSORSLEEP_LEN

| #define GICR_WAKER_PROCESSORSLEEP_LEN 1U |

◆ GICR_WAKER_PROCESSORSLEEP_OFFSET

| #define GICR_WAKER_PROCESSORSLEEP_OFFSET 1 |

◆ ICC_BPR1_EL1

| #define ICC_BPR1_EL1 "c12, c12, 3" |

◆ ICC_CTLR_EL1

| #define ICC_CTLR_EL1 "c12, c12, 4" |

◆ ICC_EOIR1_EL1

| #define ICC_EOIR1_EL1 "c12, c12, 1" |

◆ ICC_IAR1_EL1

| #define ICC_IAR1_EL1 "c12, c12, 0" |

◆ ICC_IGRPEN1_EL1

| #define ICC_IGRPEN1_EL1 "c12, c12, 7" |

◆ ICC_PMR_EL1

| #define ICC_PMR_EL1 "c4, c6, 0" |

◆ ICC_SGI1R_EL1

| #define ICC_SGI1R_EL1 "c12" |

◆ ICC_SRE_EL1

| #define ICC_SRE_EL1 "c12, c12, 5" |

◆ PRIORITY_SHIFT

| #define PRIORITY_SHIFT ((MAX_BINARY_POINT_VALUE + 1) % GIC_PRIORITY_OFFSET) |