载入中...

搜索中...

未找到

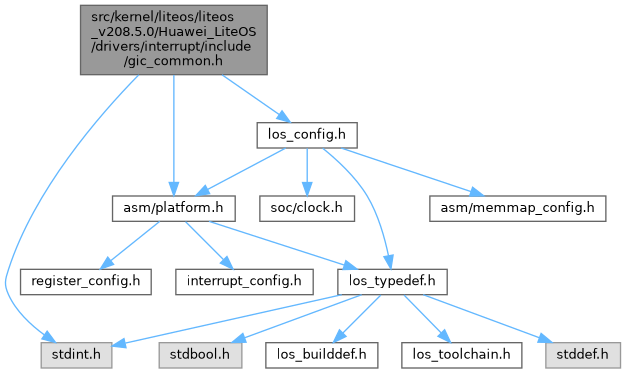

gic_common.h 的引用(Include)关系图:

宏定义 | |

| #define | TARGET_CPU_MASK 0x01010101 /* if not define TARGET_CPU_MASK,set external interrupts to CPU 0 */ |

| #define | GIC_REV_MASK 0xF0 |

| #define | GIC_REV_OFFSET 0x4 |

| #define | GICD_CTLR (GICD_OFFSET + 0x000) /* Distributor Control Register */ |

| #define | GICD_TYPER (GICD_OFFSET + 0x004) /* Interrupt Controller Type Register */ |

| #define | GICD_IIDR (GICD_OFFSET + 0x008) /* Distributor Implementer Identification Register */ |

| #define | GICD_IGROUPR(n) (GICD_OFFSET + 0x080 + (n) * 4) /* Interrupt Group Registers */ |

| #define | GICD_ISENABLER(n) (GICD_OFFSET + 0x100 + (n) * 4) /* Interrupt Set-Enable Registers */ |

| #define | GICD_ICENABLER(n) (GICD_OFFSET + 0x180 + (n) * 4) /* Interrupt Clear-Enable Registers */ |

| #define | GICD_ISPENDR(n) (GICD_OFFSET + 0x200 + (n) * 4) /* Interrupt Set-Pending Registers */ |

| #define | GICD_ICPENDR(n) (GICD_OFFSET + 0x280 + (n) * 4) /* Interrupt Clear-Pending Registers */ |

| #define | GICD_ISACTIVER(n) (GICD_OFFSET + 0x300 + (n) * 4) /* GICv2 Interrupt Set-Active Registers */ |

| #define | GICD_ICACTIVER(n) (GICD_OFFSET + 0x380 + (n) * 4) /* Interrupt Clear-Active Registers */ |

| #define | GICD_IPRIORITYR(n) (GICD_OFFSET + 0x400 + (n) * 4) /* Interrupt Priority Registers */ |

| #define | GICD_ITARGETSR(n) (GICD_OFFSET + 0x800 + (n) * 4) /* Interrupt Processor Targets Registers */ |

| #define | GICD_ICFGR(n) (GICD_OFFSET + 0xc00 + (n) * 4) /* Interrupt Configuration Registers */ |

| #define | GICD_SGIR (GICD_OFFSET + 0xf00) /* Software Generated Interrupt Register */ |

| #define | GICD_CPENDSGIR(n) (GICD_OFFSET + 0xf10 + (n) * 4) /* SGI Clear-Pending Registers; */ |

| #define | GICD_SPENDSGIR(n) (GICD_OFFSET + 0xf20 + (n) * 4) /* SGI Set-Pending Registers; */ |

| #define | GICD_PIDR2V2 (GICD_OFFSET + 0xfe8) |

| #define | GICD_PIDR2V3 (GICD_OFFSET + 0xffe8) |

| #define | GIC_REG_8(reg) (*(volatile UINT8 *)((UINTPTR)(GIC_BASE_ADDR + (reg)))) |

| #define | GIC_REG_32(reg) (*(volatile UINT32 *)((UINTPTR)(GIC_BASE_ADDR + (reg)))) |

| #define | GIC_REG_64(reg) (*(volatile UINT64 *)((UINTPTR)(GIC_BASE_ADDR + (reg)))) |

| #define | GICR_INT_DEF_PRI 0xa0U |

| #define | GICD_INT_DEF_PRI 0xa0U |

| #define | GICD_INT_DEF_PRI_X4 |

| #define | GIC_MIN_SPI_NUM 32 |

| #define | INT_COUNTS_4_PER_REG 4U /* Each register can be configured with 4 interrupts. */ |

| #define | INT_COUNTS_16_PER_REG 16U /* Each register can be configured with 16 interrupts. */ |

| #define | INT_COUNTS_32_PER_REG 32U /* Each register can be configured with 32 interrupts. */ |

| #define | BIT_SHIFT_2 2 |

| #define | BIT_SHIFT_4 4 |

| #define | BIT_SHIFT_5 5 |

枚举 | |

| enum | { GICV1 = 1 , GICV2 , GICV3 , GICV4 } |

宏定义说明

◆ BIT_SHIFT_2

| #define BIT_SHIFT_2 2 |

◆ BIT_SHIFT_4

| #define BIT_SHIFT_4 4 |

◆ BIT_SHIFT_5

| #define BIT_SHIFT_5 5 |

◆ GIC_MIN_SPI_NUM

| #define GIC_MIN_SPI_NUM 32 |

◆ GIC_REG_32

◆ GIC_REG_64

◆ GIC_REG_8

◆ GIC_REV_MASK

| #define GIC_REV_MASK 0xF0 |

◆ GIC_REV_OFFSET

| #define GIC_REV_OFFSET 0x4 |

◆ GICD_CPENDSGIR

| #define GICD_CPENDSGIR | ( | n | ) | (GICD_OFFSET + 0xf10 + (n) * 4) /* SGI Clear-Pending Registers; */ |

◆ GICD_CTLR

| #define GICD_CTLR (GICD_OFFSET + 0x000) /* Distributor Control Register */ |

◆ GICD_ICACTIVER

| #define GICD_ICACTIVER | ( | n | ) | (GICD_OFFSET + 0x380 + (n) * 4) /* Interrupt Clear-Active Registers */ |

◆ GICD_ICENABLER

| #define GICD_ICENABLER | ( | n | ) | (GICD_OFFSET + 0x180 + (n) * 4) /* Interrupt Clear-Enable Registers */ |

◆ GICD_ICFGR

| #define GICD_ICFGR | ( | n | ) | (GICD_OFFSET + 0xc00 + (n) * 4) /* Interrupt Configuration Registers */ |

◆ GICD_ICPENDR

| #define GICD_ICPENDR | ( | n | ) | (GICD_OFFSET + 0x280 + (n) * 4) /* Interrupt Clear-Pending Registers */ |

◆ GICD_IGROUPR

| #define GICD_IGROUPR | ( | n | ) | (GICD_OFFSET + 0x080 + (n) * 4) /* Interrupt Group Registers */ |

◆ GICD_IIDR

| #define GICD_IIDR (GICD_OFFSET + 0x008) /* Distributor Implementer Identification Register */ |

◆ GICD_INT_DEF_PRI

| #define GICD_INT_DEF_PRI 0xa0U |

◆ GICD_INT_DEF_PRI_X4

| #define GICD_INT_DEF_PRI_X4 |

值:

(((UINT32)GICD_INT_DEF_PRI << 24) | \

((UINT32)GICD_INT_DEF_PRI << 16) | \

((UINT32)GICD_INT_DEF_PRI << 8) | \

◆ GICD_IPRIORITYR

| #define GICD_IPRIORITYR | ( | n | ) | (GICD_OFFSET + 0x400 + (n) * 4) /* Interrupt Priority Registers */ |

◆ GICD_ISACTIVER

| #define GICD_ISACTIVER | ( | n | ) | (GICD_OFFSET + 0x300 + (n) * 4) /* GICv2 Interrupt Set-Active Registers */ |

◆ GICD_ISENABLER

| #define GICD_ISENABLER | ( | n | ) | (GICD_OFFSET + 0x100 + (n) * 4) /* Interrupt Set-Enable Registers */ |

◆ GICD_ISPENDR

| #define GICD_ISPENDR | ( | n | ) | (GICD_OFFSET + 0x200 + (n) * 4) /* Interrupt Set-Pending Registers */ |

◆ GICD_ITARGETSR

| #define GICD_ITARGETSR | ( | n | ) | (GICD_OFFSET + 0x800 + (n) * 4) /* Interrupt Processor Targets Registers */ |

◆ GICD_PIDR2V2

| #define GICD_PIDR2V2 (GICD_OFFSET + 0xfe8) |

◆ GICD_PIDR2V3

| #define GICD_PIDR2V3 (GICD_OFFSET + 0xffe8) |

◆ GICD_SGIR

| #define GICD_SGIR (GICD_OFFSET + 0xf00) /* Software Generated Interrupt Register */ |

◆ GICD_SPENDSGIR

| #define GICD_SPENDSGIR | ( | n | ) | (GICD_OFFSET + 0xf20 + (n) * 4) /* SGI Set-Pending Registers; */ |

◆ GICD_TYPER

| #define GICD_TYPER (GICD_OFFSET + 0x004) /* Interrupt Controller Type Register */ |

◆ GICR_INT_DEF_PRI

| #define GICR_INT_DEF_PRI 0xa0U |

◆ INT_COUNTS_16_PER_REG

| #define INT_COUNTS_16_PER_REG 16U /* Each register can be configured with 16 interrupts. */ |

◆ INT_COUNTS_32_PER_REG

| #define INT_COUNTS_32_PER_REG 32U /* Each register can be configured with 32 interrupts. */ |

◆ INT_COUNTS_4_PER_REG

| #define INT_COUNTS_4_PER_REG 4U /* Each register can be configured with 4 interrupts. */ |

◆ TARGET_CPU_MASK

| #define TARGET_CPU_MASK 0x01010101 /* if not define TARGET_CPU_MASK,set external interrupts to CPU 0 */ |