载入中...

搜索中...

未找到

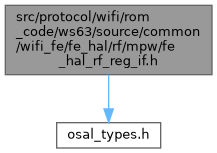

#include "osal_types.h"

fe_hal_rf_reg_if.h 的引用(Include)关系图:

类型定义 | |

| typedef osal_u8 | fe_hal_rf_reg_type_enum_uint8 |

| typedef osal_u8 | fe_hal_rf_2g_band_sel_enum_uint8 |

| typedef osal_u8 | fe_hal_rf_ctune_val_index_enum_uint8 |

宏定义说明

◆ CALI_20M_BANDWIDTH_ADJUST

| #define CALI_20M_BANDWIDTH_ADJUST 129 /* ACI刷新20M的RC CODE缩放值 */ |

◆ CALI_IQ_PHASE_SHIFT_TONE_FREQ

| #define CALI_IQ_PHASE_SHIFT_TONE_FREQ 2500 |

◆ CALI_RF_2G_UPC_PPA_BITS

| #define CALI_RF_2G_UPC_PPA_BITS 5 |

◆ CALI_RF_ADDR_SHIFT_BITS

| #define CALI_RF_ADDR_SHIFT_BITS 2 |

◆ CALI_RF_CAP_BANK_BW_I_OFST

| #define CALI_RF_CAP_BANK_BW_I_OFST BIT_OFFSET_0 |

◆ CALI_RF_CAP_BANK_BW_Q_OFST

| #define CALI_RF_CAP_BANK_BW_Q_OFST BIT_OFFSET_8 |

◆ CALI_RF_IQ_PHASE_MIN_VALUE

| #define CALI_RF_IQ_PHASE_MIN_VALUE 350 |

◆ CALI_RF_IQ_PHASE_RECT_VALUE

| #define CALI_RF_IQ_PHASE_RECT_VALUE (1 << 0xA) |

◆ CALI_RF_IQ_PHASE_THR_VALUE

| #define CALI_RF_IQ_PHASE_THR_VALUE (1 << 0x9) |

◆ CALI_RF_PA_2G_CSW_MAX_VAL

| #define CALI_RF_PA_2G_CSW_MAX_VAL 32 |

◆ CALI_RF_PA_2G_LCTUNE_MAX_VAL

| #define CALI_RF_PA_2G_LCTUNE_MAX_VAL 32 |

◆ CALI_RF_RC_CODE_BITS

| #define CALI_RF_RC_CODE_BITS 7 |

◆ CALI_RF_RC_END_OFST

| #define CALI_RF_RC_END_OFST BIT_OFFSET_15 |

◆ CALI_RF_RC_TUNE_COMP

| #define CALI_RF_RC_TUNE_COMP 1 |

◆ CALI_RF_RC_TUNE_END_BITS

| #define CALI_RF_RC_TUNE_END_BITS 1 |

◆ CALI_RF_RC_TUNE_INIT

| #define CALI_RF_RC_TUNE_INIT 0 |

◆ CALI_RF_RX_DC_DEFAULT_ANALOG_COMP

| #define CALI_RF_RX_DC_DEFAULT_ANALOG_COMP (0x8080) /* rx dc 默认的模拟补偿值 */ |

◆ CALI_RF_RX_DC_FIX_BIT

| #define CALI_RF_RX_DC_FIX_BIT (8) /* rx dc vga 最小增益值 定点化放大位数 */ |

◆ CALI_RF_RX_DC_VGA_LVL_USED_NUM

| #define CALI_RF_RX_DC_VGA_LVL_USED_NUM (1) /* rx dc补偿值vga档位数目 */ |

◆ CALI_RF_RX_DC_VGA_MAX_GAIN

| #define CALI_RF_RX_DC_VGA_MAX_GAIN (5108) /* rx dc vga 最大增益值 定点化放大 */ |

◆ CALI_RF_RX_DC_VGA_MIN_GAIN

| #define CALI_RF_RX_DC_VGA_MIN_GAIN (144) /* rx dc vga 最小增益值 定点化放大 */ |

◆ CALI_RF_RX_IQ_LVL_USED_NUM

| #define CALI_RF_RX_IQ_LVL_USED_NUM 1 |

◆ CALI_RF_TX_DC_DC3_VALUE

| #define CALI_RF_TX_DC_DC3_VALUE 0x100 /* DC3=(64mv/512mv)*2048=256 */ |

◆ CALI_RF_TX_DC_LVL_USED_NUM

| #define CALI_RF_TX_DC_LVL_USED_NUM 4 |

◆ CALI_RF_TX_IQ_LVL_USED_NUM

| #define CALI_RF_TX_IQ_LVL_USED_NUM 1 |

◆ HAL_2G_TX_PWR_VAL_MAX

| #define HAL_2G_TX_PWR_VAL_MAX (0xa0) /* ppa code限定最大值 */ |

◆ HAL_2G_TX_PWR_VAL_MIN

| #define HAL_2G_TX_PWR_VAL_MIN (0x28) /* ppa code限定最小值 */ |

◆ HAL_TXPWR_SEARCH_UPC_MAX

| #define HAL_TXPWR_SEARCH_UPC_MAX (0xc8) |

◆ HAL_TXPWR_SEARCH_UPC_MIN

| #define HAL_TXPWR_SEARCH_UPC_MIN (0x00) |

◆ HAL_TXPWR_SEARCH_UPC_STEP

| #define HAL_TXPWR_SEARCH_UPC_STEP (0x05) |

◆ HAL_TXPWR_SEARCH_UPC_TH

| #define HAL_TXPWR_SEARCH_UPC_TH (0x7F) |

◆ HH503_2G_LNA_AUTO_CONTROL

| #define HH503_2G_LNA_AUTO_CONTROL 50 |

◆ HH503_5G_LNA_AUTO_CONTROL

| #define HH503_5G_LNA_AUTO_CONTROL 96 |

◆ HH503_ADC_WL_REG0

| #define HH503_ADC_WL_REG0 396 |

◆ HH503_ADC_WL_REG1

| #define HH503_ADC_WL_REG1 397 |

◆ HH503_ADC_WL_REG2

| #define HH503_ADC_WL_REG2 398 |

◆ HH503_ADC_WL_REG3

| #define HH503_ADC_WL_REG3 399 |

◆ HH503_ADC_WL_REG4

| #define HH503_ADC_WL_REG4 400 |

◆ HH503_ADC_WL_REG5

| #define HH503_ADC_WL_REG5 401 |

◆ HH503_ADC_WL_REG6

| #define HH503_ADC_WL_REG6 402 |

◆ HH503_ADC_WL_REG7

| #define HH503_ADC_WL_REG7 403 |

◆ HH503_ADC_WL_REG8

| #define HH503_ADC_WL_REG8 404 |

◆ HH503_ADC_WL_RO_REG0

| #define HH503_ADC_WL_RO_REG0 409 |

◆ HH503_CALI_CHN_INDEX_2422

| #define HH503_CALI_CHN_INDEX_2422 0 |

◆ HH503_CALI_CHN_INDEX_2447

| #define HH503_CALI_CHN_INDEX_2447 1 |

◆ HH503_CALI_CHN_INDEX_2472

| #define HH503_CALI_CHN_INDEX_2472 2 |

◆ HH503_D_WL_LNA2G_CTUNE_LUT_REG67

| #define HH503_D_WL_LNA2G_CTUNE_LUT_REG67 67 |

◆ HH503_D_WL_LNA2G_CTUNE_LUT_REG68

| #define HH503_D_WL_LNA2G_CTUNE_LUT_REG68 68 |

◆ HH503_D_WL_LNA5G_CTUNE_LUT11_12

| #define HH503_D_WL_LNA5G_CTUNE_LUT11_12 119 |

◆ HH503_D_WL_LNA5G_CTUNE_LUT13_14

| #define HH503_D_WL_LNA5G_CTUNE_LUT13_14 120 |

◆ HH503_D_WL_LNA5G_CTUNE_LUT15_16

| #define HH503_D_WL_LNA5G_CTUNE_LUT15_16 121 |

◆ HH503_D_WL_LNA5G_CTUNE_LUT17_18

| #define HH503_D_WL_LNA5G_CTUNE_LUT17_18 122 |

◆ HH503_D_WL_LNA5G_CTUNE_LUT19_20

| #define HH503_D_WL_LNA5G_CTUNE_LUT19_20 123 |

◆ HH503_D_WL_LNA5G_CTUNE_LUT1_2

| #define HH503_D_WL_LNA5G_CTUNE_LUT1_2 114 |

◆ HH503_D_WL_LNA5G_CTUNE_LUT3_4

| #define HH503_D_WL_LNA5G_CTUNE_LUT3_4 115 |

◆ HH503_D_WL_LNA5G_CTUNE_LUT5_6

| #define HH503_D_WL_LNA5G_CTUNE_LUT5_6 116 |

◆ HH503_D_WL_LNA5G_CTUNE_LUT7_8

| #define HH503_D_WL_LNA5G_CTUNE_LUT7_8 117 |

◆ HH503_D_WL_LNA5G_CTUNE_LUT9_10

| #define HH503_D_WL_LNA5G_CTUNE_LUT9_10 118 |

◆ HH503_D_WL_LPF_CMAIN

| #define HH503_D_WL_LPF_CMAIN 144 |

◆ HH503_DAC_WL_REG0

| #define HH503_DAC_WL_REG0 405 |

◆ HH503_DAC_WL_REG1

| #define HH503_DAC_WL_REG1 406 |

◆ HH503_DAC_WL_REG2

| #define HH503_DAC_WL_REG2 407 |

◆ HH503_DAC_WL_REG3

| #define HH503_DAC_WL_REG3 408 |

◆ HH503_LOGEN_EN

| #define HH503_LOGEN_EN 6 |

◆ HH503_LOGEN_EN_REG349

| #define HH503_LOGEN_EN_REG349 349 |

◆ HH503_LOGEN_EN_REG358

| #define HH503_LOGEN_EN_REG358 358 |

◆ HH503_LOGEN_EN_REG359

| #define HH503_LOGEN_EN_REG359 359 |

◆ HH503_LOGEN_EN_REG360

| #define HH503_LOGEN_EN_REG360 360 |

◆ HH503_LOGEN_REG364

| #define HH503_LOGEN_REG364 364 |

◆ HH503_LOGEN_REG365

| #define HH503_LOGEN_REG365 365 |

◆ HH503_LOGEN_REG366

| #define HH503_LOGEN_REG366 366 |

◆ HH503_LOGEN_REG367

| #define HH503_LOGEN_REG367 367 |

◆ HH503_LOGEN_REG368

| #define HH503_LOGEN_REG368 368 |

◆ HH503_LOGEN_REG369

| #define HH503_LOGEN_REG369 369 |

◆ HH503_LOGEN_REG370

| #define HH503_LOGEN_REG370 370 |

◆ HH503_LOGEN_REG371

| #define HH503_LOGEN_REG371 371 |

◆ HH503_LOGEN_REG372

| #define HH503_LOGEN_REG372 372 |

◆ HH503_LOGEN_REG373

| #define HH503_LOGEN_REG373 373 |

◆ HH503_LOGEN_REG374

| #define HH503_LOGEN_REG374 374 |

◆ HH503_LOGEN_REG375

| #define HH503_LOGEN_REG375 375 |

◆ HH503_LOGEN_REG376

| #define HH503_LOGEN_REG376 376 |

◆ HH503_LOGEN_REG377

| #define HH503_LOGEN_REG377 377 |

◆ HH503_LOGEN_REG378

| #define HH503_LOGEN_REG378 378 |

◆ HH503_LOGEN_REG379

| #define HH503_LOGEN_REG379 379 |

◆ HH503_LOGEN_REG380

| #define HH503_LOGEN_REG380 380 |

◆ HH503_LOGEN_REG381

| #define HH503_LOGEN_REG381 381 |

◆ HH503_LPF_OP3_IBG_TRIM

| #define HH503_LPF_OP3_IBG_TRIM 148 |

◆ HH503_LPF_OP3_IBG_TRIM_REG149

| #define HH503_LPF_OP3_IBG_TRIM_REG149 149 |

◆ HH503_LPF_RX_IBG_DOUBLE1

| #define HH503_LPF_RX_IBG_DOUBLE1 150 |

◆ HH503_LPF_RX_IBG_DOUBLE2

| #define HH503_LPF_RX_IBG_DOUBLE2 151 |

◆ HH503_LPF_RX_IBG_TRIM1

| #define HH503_LPF_RX_IBG_TRIM1 146 |

◆ HH503_LPF_TX_IBG_TRIM

| #define HH503_LPF_TX_IBG_TRIM 147 |

◆ HH503_LPF_TX_QTUNE

| #define HH503_LPF_TX_QTUNE 157 |

◆ HH503_PDET_REG

| #define HH503_PDET_REG 225 |

◆ HH503_RF_2G_CHANNEL_NUM

| #define HH503_RF_2G_CHANNEL_NUM 13 |

◆ HH503_RF_2G_PPA_UPC_BITS

| #define HH503_RF_2G_PPA_UPC_BITS 5 |

◆ HH503_RF_2G_UPC_BITS

| #define HH503_RF_2G_UPC_BITS 8 |

◆ HH503_RF_2G_UPC_GC_OFST

| #define HH503_RF_2G_UPC_GC_OFST BIT_OFFSET_0 |

◆ HH503_RF_2G_UPC_PPA_2422_OFST

| #define HH503_RF_2G_UPC_PPA_2422_OFST BIT_OFFSET_0 |

◆ HH503_RF_2G_UPC_PPA_2447_OFST

| #define HH503_RF_2G_UPC_PPA_2447_OFST BIT_OFFSET_5 |

◆ HH503_RF_2G_UPC_PPA_2472_OFST

| #define HH503_RF_2G_UPC_PPA_2472_OFST BIT_OFFSET_10 |

◆ HH503_RF_2G_UPC_PPA_ENABLE_BITS

| #define HH503_RF_2G_UPC_PPA_ENABLE_BITS 2 |

◆ HH503_RF_BAND_INFO_BITS

| #define HH503_RF_BAND_INFO_BITS 3 |

◆ HH503_RF_BAND_INFO_OFST

| #define HH503_RF_BAND_INFO_OFST BIT_OFFSET_0 |

◆ HH503_RF_BAND_WIDTH_BITS

| #define HH503_RF_BAND_WIDTH_BITS 1 |

◆ HH503_RF_BAND_WIDTH_OFST

| #define HH503_RF_BAND_WIDTH_OFST BIT_OFFSET_0 |

◆ HH503_RF_DAC_GAIN_DEFAULT_VAL

| #define HH503_RF_DAC_GAIN_DEFAULT_VAL 0x24 |

◆ HH503_RF_FREQ_2_CHANNEL_NUM

| #define HH503_RF_FREQ_2_CHANNEL_NUM 14 /* 2g支持信道数目 */ |

◆ HH503_RF_FREQ_5_CHANNEL_NUM

| #define HH503_RF_FREQ_5_CHANNEL_NUM 29 /* 5g支持信道数目 */ |

◆ HH503_RF_LPF_GAIN_DEFAULT_VAL

| #define HH503_RF_LPF_GAIN_DEFAULT_VAL 0x4688 |

◆ HH503_RF_RX_PPF_OFST

| #define HH503_RF_RX_PPF_OFST BIT_OFFSET_12 |

◆ HH503_RF_TEMP_INVALID

| #define HH503_RF_TEMP_INVALID (-100) /* 温度非法值 */ |

◆ HH503_RF_TEMP_STS_RSV

| #define HH503_RF_TEMP_STS_RSV 0x7 |

◆ HH503_RF_W_C0_CTL_ABB_CLK_WL_AD_DIV_GT_C0_REG

| #define HH503_RF_W_C0_CTL_ABB_CLK_WL_AD_DIV_GT_C0_REG (HH503_RF_W_C0_CTL_BASE + 0x220) |

◆ HH503_RF_W_C0_CTL_ABB_CLK_WL_DA_DIV_GT_C0_REG

| #define HH503_RF_W_C0_CTL_ABB_CLK_WL_DA_DIV_GT_C0_REG (HH503_RF_W_C0_CTL_BASE + 0x230) |

◆ HH503_RF_W_C0_CTL_ABB_WL_ADC_C0_MAN_REG

| #define HH503_RF_W_C0_CTL_ABB_WL_ADC_C0_MAN_REG (HH503_RF_W_C0_CTL_BASE + 0x200) |

◆ HH503_RF_W_C0_CTL_ABB_WL_ADC_C0_SEL_REG

| #define HH503_RF_W_C0_CTL_ABB_WL_ADC_C0_SEL_REG (HH503_RF_W_C0_CTL_BASE + 0x204) |

◆ HH503_RF_W_C0_CTL_ABB_WL_DAC_C0_MAN_REG

| #define HH503_RF_W_C0_CTL_ABB_WL_DAC_C0_MAN_REG (HH503_RF_W_C0_CTL_BASE + 0x210) |

◆ HH503_RF_W_C0_CTL_ABB_WL_DAC_C0_SEL_REG

| #define HH503_RF_W_C0_CTL_ABB_WL_DAC_C0_SEL_REG (HH503_RF_W_C0_CTL_BASE + 0x218) |

◆ HH503_RF_W_C0_CTL_BASE

| #define HH503_RF_W_C0_CTL_BASE 0x40040000 |

◆ HH503_RF_W_C0_CTL_WL_TRX_MAN_C0_REG

| #define HH503_RF_W_C0_CTL_WL_TRX_MAN_C0_REG (HH503_RF_W_C0_CTL_BASE + 0x110) |

◆ HH503_RF_W_C0_CTL_WL_TRX_MAN_C1_REG

| #define HH503_RF_W_C0_CTL_WL_TRX_MAN_C1_REG (HH503_RF_W_C1_CTL_BASE + 0x110) |

◆ HH503_RF_W_C0_CTL_WL_TRX_SEL_C0_REG

| #define HH503_RF_W_C0_CTL_WL_TRX_SEL_C0_REG (HH503_RF_W_C0_CTL_BASE + 0x114) |

◆ HH503_RF_W_C0_CTL_WL_TRX_SEL_C1_REG

| #define HH503_RF_W_C0_CTL_WL_TRX_SEL_C1_REG (HH503_RF_W_C1_CTL_BASE + 0x114) |

◆ HH503_RF_W_C0_REG_BASE_ADDR

| #define HH503_RF_W_C0_REG_BASE_ADDR 0x40040800 |

◆ HH503_RF_W_C1_CTL_ABB_CLK_WL_AD_DIV_GT_C1_REG

| #define HH503_RF_W_C1_CTL_ABB_CLK_WL_AD_DIV_GT_C1_REG (HH503_RF_W_C1_CTL_BASE + 0x220) |

◆ HH503_RF_W_C1_CTL_ABB_CLK_WL_DA_DIV_GT_C1_REG

| #define HH503_RF_W_C1_CTL_ABB_CLK_WL_DA_DIV_GT_C1_REG (HH503_RF_W_C1_CTL_BASE + 0x230) |

◆ HH503_RF_W_C1_CTL_ABB_WL_ADC_C1_MAN_REG

| #define HH503_RF_W_C1_CTL_ABB_WL_ADC_C1_MAN_REG (HH503_RF_W_C1_CTL_BASE + 0x200) |

◆ HH503_RF_W_C1_CTL_ABB_WL_ADC_C1_SEL_REG

| #define HH503_RF_W_C1_CTL_ABB_WL_ADC_C1_SEL_REG (HH503_RF_W_C1_CTL_BASE + 0x204) |

◆ HH503_RF_W_C1_CTL_ABB_WL_DAC_C1_MAN_REG

| #define HH503_RF_W_C1_CTL_ABB_WL_DAC_C1_MAN_REG (HH503_RF_W_C1_CTL_BASE + 0x210) |

◆ HH503_RF_W_C1_CTL_ABB_WL_DAC_C1_SEL_REG

| #define HH503_RF_W_C1_CTL_ABB_WL_DAC_C1_SEL_REG (HH503_RF_W_C1_CTL_BASE + 0x218) |

◆ HH503_RF_W_C1_CTL_BASE

| #define HH503_RF_W_C1_CTL_BASE 0x40042000 |

◆ HH503_RF_W_C1_REG_BASE_ADDR

| #define HH503_RF_W_C1_REG_BASE_ADDR 0x40042800 |

◆ HH503_RF_W_PLL_C0_REG_BASE_ADDR

| #define HH503_RF_W_PLL_C0_REG_BASE_ADDR 0x40041000 |

◆ HH503_RF_W_PLL_C1_REG_BASE_ADDR

| #define HH503_RF_W_PLL_C1_REG_BASE_ADDR 0x40043000 |

◆ HH503_RX2G_LO_DIV_EN_CTRL_REG89

| #define HH503_RX2G_LO_DIV_EN_CTRL_REG89 89 |

◆ HH503_RX2G_LO_DIV_LODIV_CAL_O_REG91

| #define HH503_RX2G_LO_DIV_LODIV_CAL_O_REG91 91 |

◆ HH503_TEMPERATURE_THRESH

| #define HH503_TEMPERATURE_THRESH 50 |

◆ HH503_TOP_TST_SW1

| #define HH503_TOP_TST_SW1 29 |

◆ HH503_TOP_TST_SW2

| #define HH503_TOP_TST_SW2 30 |

◆ HH503_TX2G_BIAS_CURRENT_EN

| #define HH503_TX2G_BIAS_CURRENT_EN 233 |

◆ HH503_TX2G_CURRENT_CAL_REG47

| #define HH503_TX2G_CURRENT_CAL_REG47 47 |

◆ HH503_TX2G_CURRENT_CAL_REG48

| #define HH503_TX2G_CURRENT_CAL_REG48 48 |

◆ HH503_TX2G_LO_DIV_LODIV_CAL_O_REG287

| #define HH503_TX2G_LO_DIV_LODIV_CAL_O_REG287 287 |

◆ HH503_TX2G_PA_CTL_REG289

| #define HH503_TX2G_PA_CTL_REG289 289 |

◆ HH503_TX2G_PA_CTL_REG290

| #define HH503_TX2G_PA_CTL_REG290 290 |

◆ HH503_TX2G_PA_CTL_REG291

| #define HH503_TX2G_PA_CTL_REG291 291 |

◆ HH503_TX2G_PA_CTL_REG292

| #define HH503_TX2G_PA_CTL_REG292 292 |

◆ HH503_TX2G_PA_CTL_REG293

| #define HH503_TX2G_PA_CTL_REG293 293 |

◆ HH503_TX2G_PA_CURRENT_TRIM

| #define HH503_TX2G_PA_CURRENT_TRIM 294 |

◆ HH503_TX2G_PA_CURRENT_TRIM_B

| #define HH503_TX2G_PA_CURRENT_TRIM_B 295 |

◆ HH503_TX2G_PA_GAINCTL

| #define HH503_TX2G_PA_GAINCTL 35 |

◆ HH503_TX2G_PA_GATE_VCTL_REG236

| #define HH503_TX2G_PA_GATE_VCTL_REG236 236 |

◆ HH503_TX2G_PA_GATE_VCTL_REG237

| #define HH503_TX2G_PA_GATE_VCTL_REG237 237 |

◆ HH503_TX2G_PA_GATE_VCTL_REG238

| #define HH503_TX2G_PA_GATE_VCTL_REG238 238 |

◆ HH503_TX2G_PA_GATE_VCTL_REG239

| #define HH503_TX2G_PA_GATE_VCTL_REG239 239 |

◆ HH503_TX2G_PA_GATE_VCTL_REG240

| #define HH503_TX2G_PA_GATE_VCTL_REG240 240 |

◆ HH503_TX2G_PA_GATE_VCTL_REG241

| #define HH503_TX2G_PA_GATE_VCTL_REG241 241 |

◆ HH503_TX2G_PA_GATE_VCTL_REG242

| #define HH503_TX2G_PA_GATE_VCTL_REG242 242 |

◆ HH503_TX2G_PA_GATE_VCTL_REG243

| #define HH503_TX2G_PA_GATE_VCTL_REG243 243 |

◆ HH503_TX2G_PA_GATE_VCTL_REG244

| #define HH503_TX2G_PA_GATE_VCTL_REG244 244 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG253

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG253 253 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG254

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG254 254 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG255

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG255 255 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG256

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG256 256 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG257

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG257 257 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG258

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG258 258 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG259

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG259 259 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG260

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG260 260 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG261

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG261 261 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG262

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG262 262 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG263

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG263 263 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG264

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG264 264 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG265

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG265 265 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG266

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG266 266 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG267

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG267 267 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG268

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG268 268 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG269

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG269 269 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG270

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG270 270 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG271

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG271 271 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG272

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG272 272 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG273

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG273 273 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG274

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG274 274 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG275

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG275 275 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG276

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG276 276 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG277

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG277 277 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG278

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG278 278 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG279

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG279 279 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG280

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG280 280 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG281

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG281 281 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG282

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG282 282 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG283

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG283 283 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG284

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG284 284 |

◆ HH503_TX2G_PA_VRECT_GATE_THIN_REG286

| #define HH503_TX2G_PA_VRECT_GATE_THIN_REG286 286 |

◆ HH503_TX2G_PPA_VC_CTL

| #define HH503_TX2G_PPA_VC_CTL 32 |

◆ HH503_TX2G_PPA_VC_SW

| #define HH503_TX2G_PPA_VC_SW 33 |

◆ HH503_TX2G_RESERVE_CTRL_1

| #define HH503_TX2G_RESERVE_CTRL_1 296 |

◆ HH503_TX2G_RESERVE_CTRL_2

| #define HH503_TX2G_RESERVE_CTRL_2 297 |

◆ HH503_TX2G_RESERVE_CTRL_3

| #define HH503_TX2G_RESERVE_CTRL_3 298 |

◆ HH503_TX2G_RESERVE_CTRL_4

| #define HH503_TX2G_RESERVE_CTRL_4 299 |

◆ HH503_TX5G_UPC_MIX_GAIN_CTRL_1

| #define HH503_TX5G_UPC_MIX_GAIN_CTRL_1 300 |

◆ HH503_TX5G_UPC_MIX_GAIN_CTRL_2

| #define HH503_TX5G_UPC_MIX_GAIN_CTRL_2 301 |

◆ HH503_TX5G_UPC_MIX_GAIN_CTRL_3

| #define HH503_TX5G_UPC_MIX_GAIN_CTRL_3 302 |

◆ HH503_TX5G_UPC_MIX_GAIN_CTRL_4

| #define HH503_TX5G_UPC_MIX_GAIN_CTRL_4 303 |

◆ HH503_TX5G_UPC_MIX_GAIN_CTRL_5

| #define HH503_TX5G_UPC_MIX_GAIN_CTRL_5 304 |

◆ HH503_TX5G_UPC_MIX_GAIN_CTRL_6

| #define HH503_TX5G_UPC_MIX_GAIN_CTRL_6 305 |

◆ HH503_TX5G_UPC_MIX_GAIN_CTRL_7

| #define HH503_TX5G_UPC_MIX_GAIN_CTRL_7 306 |

◆ HH503_VGA_BW_RP

| #define HH503_VGA_BW_RP 226 |

◆ HH503_VGA_CC_CTRL_NORMAL_TT4

| #define HH503_VGA_CC_CTRL_NORMAL_TT4 187 |

◆ HH503_VGA_CC_CTRL_NORMAL_TT5

| #define HH503_VGA_CC_CTRL_NORMAL_TT5 188 |

◆ HH503_VGA_CFB_CTRL_NORMAL_TT2

| #define HH503_VGA_CFB_CTRL_NORMAL_TT2 176 |

◆ HH503_VGA_ITRIM

| #define HH503_VGA_ITRIM 162 |

◆ HH503_VGA_ITRIM_DOUBLE

| #define HH503_VGA_ITRIM_DOUBLE 164 |

◆ HH503_VGA_RZ_TT2

| #define HH503_VGA_RZ_TT2 170 |

◆ HH503_WL_BAND_SEL

| #define HH503_WL_BAND_SEL 12 |

◆ HH503_WL_C_R_CODE

| #define HH503_WL_C_R_CODE 14 |

◆ HH503_WL_CALI_MODULES_EN_REG7

| #define HH503_WL_CALI_MODULES_EN_REG7 7 |

◆ HH503_WL_CALI_MODULES_EN_REG8

| #define HH503_WL_CALI_MODULES_EN_REG8 8 |

◆ HH503_WL_LPF_BW

| #define HH503_WL_LPF_BW 19 |

◆ HH503_WL_RX_AGC_CTRL

| #define HH503_WL_RX_AGC_CTRL 10 |

◆ HH503_WL_RX_DCOC

| #define HH503_WL_RX_DCOC 20 |

◆ HH503_WL_RX_DIVIDER_REG90

| #define HH503_WL_RX_DIVIDER_REG90 90 |

◆ HH503_WL_RX_MODULES_EN

| #define HH503_WL_RX_MODULES_EN 4 |

◆ HH503_WL_RX_RC_CODE

| #define HH503_WL_RX_RC_CODE 15 |

◆ HH503_WL_RX_RC_CODE_VGA_REG17

| #define HH503_WL_RX_RC_CODE_VGA_REG17 17 |

◆ HH503_WL_RX_RC_CODE_VGA_REG18

| #define HH503_WL_RX_RC_CODE_VGA_REG18 18 |

◆ HH503_WL_RX_TST_MODE

| #define HH503_WL_RX_TST_MODE 21 |

◆ HH503_WL_TEMP_CODE

| #define HH503_WL_TEMP_CODE 13 |

◆ HH503_WL_TOP_RESERVED

| #define HH503_WL_TOP_RESERVED 31 |

◆ HH503_WL_TRX_ENABLE_REG0

| #define HH503_WL_TRX_ENABLE_REG0 0 |

◆ HH503_WL_TRX_ENABLE_REG1

| #define HH503_WL_TRX_ENABLE_REG1 1 |

◆ HH503_WL_TRX_ENABLE_REG2

| #define HH503_WL_TRX_ENABLE_REG2 2 |

◆ HH503_WL_TRX_ENABLE_REG3

| #define HH503_WL_TRX_ENABLE_REG3 3 |

◆ HH503_WL_TRX_ENABLE_REG9

| #define HH503_WL_TRX_ENABLE_REG9 9 |

◆ HH503_WL_TST_BUF

| #define HH503_WL_TST_BUF 28 |

◆ HH503_WL_TST_SW1

| #define HH503_WL_TST_SW1 25 |

◆ HH503_WL_TST_SW2_REG26

| #define HH503_WL_TST_SW2_REG26 26 |

◆ HH503_WL_TST_SW2_REG27

| #define HH503_WL_TST_SW2_REG27 27 |

◆ HH503_WL_TX_GAIN_CTRL

| #define HH503_WL_TX_GAIN_CTRL 11 |

◆ HH503_WL_TX_MODULES_EN

| #define HH503_WL_TX_MODULES_EN 5 |

◆ HH503_WL_TX_PDET2G_CTRL_REG340

| #define HH503_WL_TX_PDET2G_CTRL_REG340 340 |

◆ HH503_WL_TX_PDET2G_CTRL_REG341

| #define HH503_WL_TX_PDET2G_CTRL_REG341 341 |

◆ HH503_WL_TX_PDET2G_CTRL_REG342

| #define HH503_WL_TX_PDET2G_CTRL_REG342 342 |

◆ HH503_WL_TX_RC_CODE

| #define HH503_WL_TX_RC_CODE 16 |

◆ HH503_WL_TX_TST_MODE

| #define HH503_WL_TX_TST_MODE 22 |

◆ HH503_WL_TX_UPC5_LC_TANK_REG43

| #define HH503_WL_TX_UPC5_LC_TANK_REG43 43 |

◆ HH503_WL_TX_UPC5_LC_TANK_REG44

| #define HH503_WL_TX_UPC5_LC_TANK_REG44 44 |

◆ HH503_WL_TX_UPC5_LC_TANK_REG45

| #define HH503_WL_TX_UPC5_LC_TANK_REG45 45 |

◆ HH503_WL_TX_UPC5_LC_TANK_REG46

| #define HH503_WL_TX_UPC5_LC_TANK_REG46 46 |

◆ HH503_WL_TX_UPC5_PPAGAIN_CTRL_REG36

| #define HH503_WL_TX_UPC5_PPAGAIN_CTRL_REG36 36 |

◆ HH503_WL_TX_UPC5_PPAGAIN_CTRL_REG37

| #define HH503_WL_TX_UPC5_PPAGAIN_CTRL_REG37 37 |

◆ HH503_WL_TX_UPC5_PPAGAIN_CTRL_REG38

| #define HH503_WL_TX_UPC5_PPAGAIN_CTRL_REG38 38 |

◆ HH503_WL_TX_UPC5_PPAGAIN_CTRL_REG39

| #define HH503_WL_TX_UPC5_PPAGAIN_CTRL_REG39 39 |

◆ HH503_WL_TX_UPC5_PPAGAIN_CTRL_REG40

| #define HH503_WL_TX_UPC5_PPAGAIN_CTRL_REG40 40 |

◆ HH503_WL_TX_UPC5_PPAGAIN_CTRL_REG41

| #define HH503_WL_TX_UPC5_PPAGAIN_CTRL_REG41 41 |

◆ HH503_WL_TX_UPC5_PPAGAIN_CTRL_REG42

| #define HH503_WL_TX_UPC5_PPAGAIN_CTRL_REG42 42 |

◆ HH503_WL_VGA_ITRIM

| #define HH503_WL_VGA_ITRIM 229 |

◆ RF_CALI_DATA_BUF_LEN

| #define RF_CALI_DATA_BUF_LEN (0x6cd8) |

◆ RF_SINGLE_CHAN_CALI_DATA_BUF_LEN

| #define RF_SINGLE_CHAN_CALI_DATA_BUF_LEN (RF_CALI_DATA_BUF_LEN >> 1) |

类型定义说明

◆ fe_hal_rf_2g_band_sel_enum_uint8

◆ fe_hal_rf_ctune_val_index_enum_uint8

◆ fe_hal_rf_reg_type_enum_uint8

| typedef osal_u8 fe_hal_rf_reg_type_enum_uint8 |