载入中...

搜索中...

未找到

#include "osal_types.h"

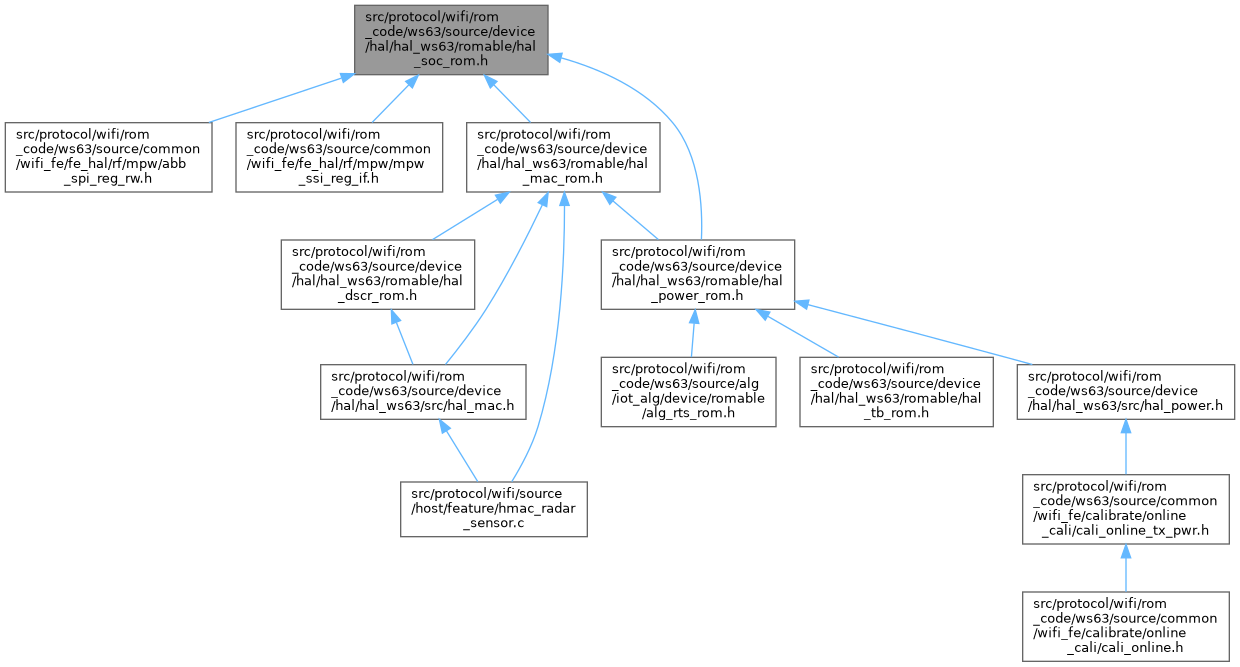

hal_soc_rom.h 的引用(Include)关系图:

此图展示该文件直接或间接的被哪些文件引用了:

枚举 | |

| enum | hh503_soc_bank_idx_enum { WITP_SOC_BANK_0 = 0 , WITP_SOC_RF_W_C0_CTL_1 , WITP_SOC_RF_W_C1_CTL_2 , WITP_SOC_W_CTL_3 , WITP_SOC_COEX_CTL_4 , WITP_SOC_BANK_BUTT } |

宏定义说明

◆ HH503_CFG_FREQ_BUSDMAC

| #define HH503_CFG_FREQ_BUSDMAC (HH503_SHARE_MEM__CTL_ID + 0x50) |

◆ HH503_CFG_RX_DONE_ADDR

| #define HH503_CFG_RX_DONE_ADDR (HH503_SHARE_MEM__CTL_ID + 0x68) |

◆ HH503_CFG_RX_DONE_STS

| #define HH503_CFG_RX_DONE_STS (HH503_SHARE_MEM__CTL_ID + 0x64) |

◆ HH503_CFG_RX_EN

| #define HH503_CFG_RX_EN (HH503_SHARE_MEM__CTL_ID + 0x58) |

◆ HH503_CFG_RX_END_ADDR

| #define HH503_CFG_RX_END_ADDR (HH503_SHARE_MEM__CTL_ID + 0x60) |

◆ HH503_CFG_RX_START_ADDR

| #define HH503_CFG_RX_START_ADDR (HH503_SHARE_MEM__CTL_ID + 0x5c) |

◆ HH503_CFG_TX_DONE_ADDR

| #define HH503_CFG_TX_DONE_ADDR (HH503_SHARE_MEM__CTL_ID + 0x80) |

◆ HH503_CFG_TX_DONE_STS

| #define HH503_CFG_TX_DONE_STS (HH503_SHARE_MEM__CTL_ID + 0x7c) |

◆ HH503_CFG_TX_EN

| #define HH503_CFG_TX_EN (HH503_SHARE_MEM__CTL_ID + 0x70) |

◆ HH503_CFG_TX_END_ADDR

| #define HH503_CFG_TX_END_ADDR (HH503_SHARE_MEM__CTL_ID + 0x78) |

◆ HH503_CFG_TX_START_ADDR

| #define HH503_CFG_TX_START_ADDR (HH503_SHARE_MEM__CTL_ID + 0x74) |

◆ HH503_CFG_WLPHY2PKT_RX_RAM_STS

| #define HH503_CFG_WLPHY2PKT_RX_RAM_STS (HH503_SHARE_MEM__CTL_ID + 0x6c) |

◆ HH503_CFG_WLPHY2PKT_TX_RAM_STS

| #define HH503_CFG_WLPHY2PKT_TX_RAM_STS (HH503_SHARE_MEM__CTL_ID + 0x84) |

◆ HH503_SHARE_MEM__CTL_ID

| #define HH503_SHARE_MEM__CTL_ID 0x44006c00 |

◆ HH503_SPI0_0_BASE_ADDR

| #define HH503_SPI0_0_BASE_ADDR (HH503_SSI0_MST_RB_BASE_ADDR + 0x800) /* WL0 ADDA */ |

◆ HH503_SPI0_1_BASE_ADDR

| #define HH503_SPI0_1_BASE_ADDR (HH503_SSI0_MST_RB_BASE_ADDR + 0xA00) /* WL1 ADDA */ |

◆ HH503_SPI0_2_BASE_ADDR

| #define HH503_SPI0_2_BASE_ADDR (HH503_SSI0_MST_RB_BASE_ADDR + 0xC00) /* ABB5_0 PLL */ |

◆ HH503_SSI0_MST_RB_BASE_ADDR

| #define HH503_SSI0_MST_RB_BASE_ADDR 0x44030000 |

◆ HH503_SSI0_MST_RB_RW_REG1_REG

| #define HH503_SSI0_MST_RB_RW_REG1_REG (HH503_SSI0_MST_RB_BASE_ADDR + 0x1A4) |

◆ HH503_SSI0_MST_RB_SSI_MST_CK_CFG_REG

| #define HH503_SSI0_MST_RB_SSI_MST_CK_CFG_REG (HH503_SSI0_MST_RB_BASE_ADDR + 0x4C) /* SSI0 ctrl */ |

◆ HH503_SSI1_MST_RB_BASE_ADDR

| #define HH503_SSI1_MST_RB_BASE_ADDR (HH503_SSI0_MST_RB_BASE_ADDR + 0x400) |

◆ HH503_SSI1_MST_RB_RW_REG1_REG

| #define HH503_SSI1_MST_RB_RW_REG1_REG (HH503_SSI1_MST_RB_BASE_ADDR + 0x1A4) |

◆ HH503_SSI1_MST_RB_SSI_MST_CK_CFG_REG

| #define HH503_SSI1_MST_RB_SSI_MST_CK_CFG_REG (HH503_SSI1_MST_RB_BASE_ADDR + 0x4C) /* SSI1 ctrl */ |