载入中...

搜索中...

未找到

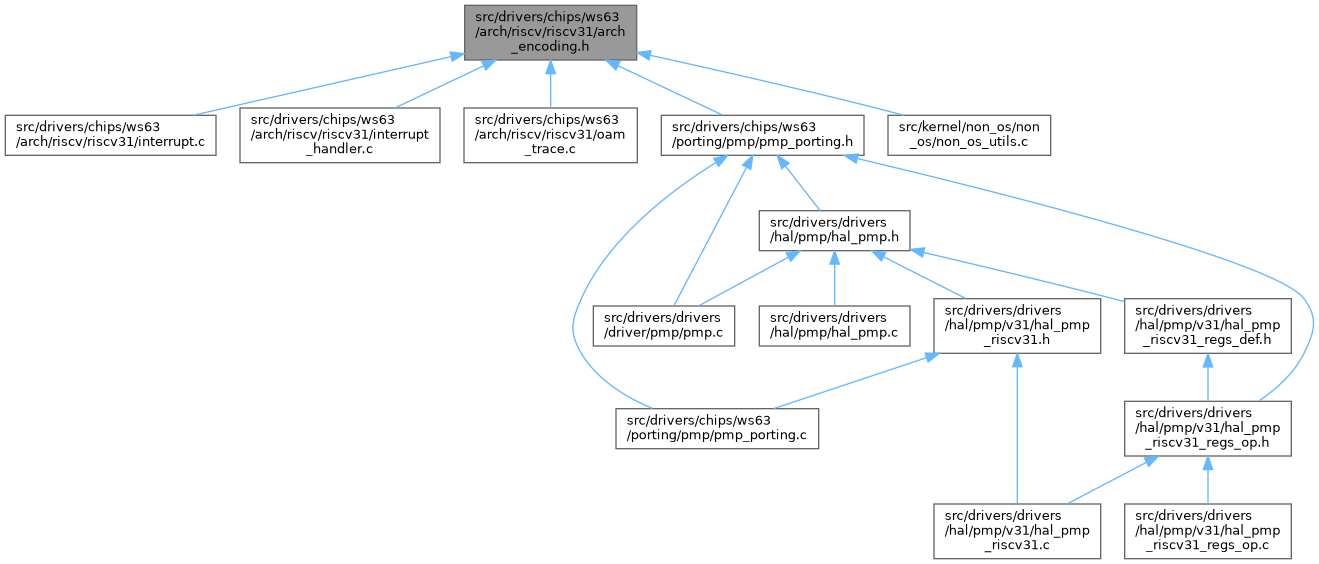

arch_encoding.h 文件参考

此图展示该文件直接或间接的被哪些文件引用了:

宏定义 | |

| #define | MCAUSE 0x342 |

| #define | MCAUSE_INSN_MISALIGN 0x0 |

| #define | MCAUSE_INSN_FAULT 0x1 |

| #define | MCAUSE_INSN_ILLEGAL 0x2 |

| #define | MCAUSE_BRKT 0x3 |

| #define | MCSUSE_LOAD_MISALIGN 0x4 |

| #define | MCAUSE_LOAD_FAULT 0x5 |

| #define | MCAUSE_AMO_MISALIGN 0x6 |

| #define | MCAUSE_AMO_FAULT 0x7 |

| #define | MCAUSE_ECALL_U 0x8 |

| #define | MCAUSE_ECALL_M 0xB |

| #define | MCAUSE_INSN_PAGE_FAULT 0xC |

| #define | MCAUSE_LOAD_PAGE_FAULT 0xD |

| #define | MCAUSE_AMO_PAGE_FAULT 0xF |

| #define | EXC_SIZE_ON_STACK (160) |

| #define | MSTATUS_UIE 0x00000001 |

| #define | MSTATUS_SIE 0x00000002 |

| #define | MSTATUS_HIE 0x00000004 |

| #define | MSTATUS_MIE 0x00000008 |

| #define | MSTATUS_UPIE 0x00000010 |

| #define | MSTATUS_SPIE 0x00000020 |

| #define | MSTATUS_HPIE 0x00000040 |

| #define | MSTATUS_MPIE 0x00000080 |

| #define | MSTATUS_SPP 0x00000100 |

| #define | MSTATUS_HPP 0x00000600 |

| #define | MSTATUS_MPP 0x00001800 |

| #define | MSTATUS_FS 0x00006000 |

| #define | MSTATUS_XS 0x00018000 |

| #define | MSTATUS_MPRV 0x00020000 |

| #define | MSTATUS_PUM 0x00040000 |

| #define | MSTATUS_VM 0x1F000000 |

| #define | MSTATUS32_SD 0x80000000 |

| #define | MSTATUS64_SD 0x8000000000000000 |

| #define | MCAUSE32_CAUSE 0x7FFFFFFF |

| #define | MCAUSE64_CAUSE 0x7FFFFFFFFFFFFFFF |

| #define | MCAUSE32_INT 0x80000000 |

| #define | MCAUSE64_INT 0x8000000000000000 |

| #define | SSTATUS_UIE 0x00000001 |

| #define | SSTATUS_SIE 0x00000002 |

| #define | SSTATUS_UPIE 0x00000010 |

| #define | SSTATUS_SPIE 0x00000020 |

| #define | SSTATUS_SPP 0x00000100 |

| #define | SSTATUS_FS 0x00006000 |

| #define | SSTATUS_XS 0x00018000 |

| #define | SSTATUS_PUM 0x00040000 |

| #define | SSTATUS32_SD 0x80000000 |

| #define | SSTATUS64_SD 0x8000000000000000 |

| #define | IRQ_S_SOFT 1 |

| #define | IRQ_H_SOFT 2 |

| #define | IRQ_M_SOFT 3 |

| #define | IRQ_S_TIMER 5 |

| #define | IRQ_H_TIMER 6 |

| #define | IRQ_M_TIMER 7 |

| #define | IRQ_S_EXT 9 |

| #define | IRQ_H_EXT 10 |

| #define | IRQ_M_EXT 11 |

| #define | IRQ_COP 12 |

| #define | IRQ_HOST 13 |

| #define | IRQ_LOCIE0 26 |

| #define | IRQ_LOCIE1 27 |

| #define | IRQ_LOCIE2 28 |

| #define | IRQ_LOCIE3 29 |

| #define | IRQ_LOCIE4 30 |

| #define | IRQ_LOCIE5 31 |

| #define | IRQ_LOCIE6 0 |

| #define | IRQ_LOCIE7 1 |

| #define | IRQ_LOCIE8 2 |

| #define | IRQ_LOCIE9 3 |

| #define | IRQ_LOCIE10 4 |

| #define | IRQ_LOCIE11 5 |

| #define | IRQ_LOCIE12 6 |

| #define | IRQ_LOCIE13 7 |

| #define | IRQ_LOCIE14 8 |

| #define | IRQ_LOCIE15 9 |

| #define | IRQ_LOCIE16 10 |

| #define | IRQ_LOCIE17 11 |

| #define | IRQ_LOCIE18 12 |

| #define | IRQ_LOCIE19 13 |

| #define | IRQ_LOCIE20 14 |

| #define | IRQ_LOCIE21 15 |

| #define | IRQ_LOCIE22 16 |

| #define | IRQ_LOCIE23 17 |

| #define | IRQ_LOCIE24 18 |

| #define | IRQ_LOCIE25 19 |

| #define | IRQ_LOCIE26 20 |

| #define | IRQ_LOCIE27 21 |

| #define | IRQ_LOCIE28 22 |

| #define | IRQ_LOCIE29 23 |

| #define | IRQ_LOCIE30 24 |

| #define | IRQ_LOCIE31 25 |

| #define | IRQ_NMI 12 |

| #define | MIP_NMI (1 << IRQ_NMI) |

| #define | MIP_SSIE (1 << IRQ_S_SOFT) |

| #define | MIP_HSIE (1 << IRQ_H_SOFT) |

| #define | MIP_MSIE (1 << IRQ_M_SOFT) |

| #define | MIP_STIE (1 << IRQ_S_TIMER) |

| #define | MIP_HTIE (1 << IRQ_H_TIMER) |

| #define | MIP_MTIE (1 << IRQ_M_TIMER) |

| #define | MIP_SEIE (1 << IRQ_S_EXT) |

| #define | MIP_HEIE (1 << IRQ_H_EXT) |

| #define | MIP_MEIE (1 << IRQ_M_EXT) |

| #define | MIP_NMIE (1 << IRQ_COP) |

| #define | MIP_LOCIE0 (1 << IRQ_LOCIE0) |

| #define | MIP_LOCIE1 (1 << IRQ_LOCIE1) |

| #define | MIP_LOCIE2 (1 << IRQ_LOCIE2) |

| #define | MIP_LOCIE3 (1 << IRQ_LOCIE3) |

| #define | MIP_LOCIE4 (1 << IRQ_LOCIE4) |

| #define | MIP_LOCIE5 ((uint32_t)1 << IRQ_LOCIE5) |

| #define | LOCIPD0_LOCIE6 (1 << IRQ_LOCIE6) |

| #define | LOCIPD0_LOCIE7 (1 << IRQ_LOCIE7) |

| #define | LOCIPD0_LOCIE8 (1 << IRQ_LOCIE8) |

| #define | LOCIPD0_LOCIE9 (1 << IRQ_LOCIE9) |

| #define | LOCIPD0_LOCIE10 (1 << IRQ_LOCIE10) |

| #define | LOCIPD0_LOCIE11 (1 << IRQ_LOCIE11) |

| #define | LOCIPD0_LOCIE12 (1 << IRQ_LOCIE12) |

| #define | LOCIPD0_LOCIE13 (1 << IRQ_LOCIE13) |

| #define | LOCIPD0_LOCIE14 (1 << IRQ_LOCIE14) |

| #define | LOCIPD0_LOCIE15 (1 << IRQ_LOCIE15) |

| #define | LOCIPD0_LOCIE16 (1 << IRQ_LOCIE16) |

| #define | LOCIPD0_LOCIE17 (1 << IRQ_LOCIE17) |

| #define | LOCIPD0_LOCIE18 (1 << IRQ_LOCIE18) |

| #define | LOCIPD0_LOCIE19 (1 << IRQ_LOCIE19) |

| #define | LOCIPD0_LOCIE20 (1 << IRQ_LOCIE20) |

| #define | LOCIPD0_LOCIE21 (1 << IRQ_LOCIE21) |

| #define | LOCIPD0_LOCIE22 (1 << IRQ_LOCIE22) |

| #define | LOCIPD0_LOCIE23 (1 << IRQ_LOCIE23) |

| #define | LOCIPD0_LOCIE24 (1 << IRQ_LOCIE24) |

| #define | LOCIPD0_LOCIE25 (1 << IRQ_LOCIE25) |

| #define | LOCIPD0_LOCIE26 (1 << IRQ_LOCIE26) |

| #define | LOCIPD0_LOCIE27 (1 << IRQ_LOCIE27) |

| #define | LOCIPD0_LOCIE28 (1 << IRQ_LOCIE28) |

| #define | LOCIPD0_LOCIE29 (1 << IRQ_LOCIE29) |

| #define | LOCIPD0_LOCIE30 (1 << IRQ_LOCIE30) |

| #define | LOCIPD0_LOCIE31 (1 << IRQ_LOCIE31) |

| #define | PMPCFG0 0 |

| #define | PMPCFG1 1 |

| #define | PMPCFG2 2 |

| #define | PMPCFG3 3 |

| #define | PMPADDR0 0 |

| #define | PMPADDR1 1 |

| #define | PMPADDR2 2 |

| #define | PMPADDR3 3 |

| #define | PMPADDR4 4 |

| #define | PMPADDR5 5 |

| #define | PMPADDR6 6 |

| #define | PMPADDR7 7 |

| #define | PMPADDR8 8 |

| #define | PMPADDR9 9 |

| #define | PMPADDR10 10 |

| #define | PMPADDR11 11 |

| #define | PMPADDR12 12 |

| #define | PMPADDR13 13 |

| #define | PMPADDR14 14 |

| #define | PMPADDR15 15 |

| #define | LOCIPRI0 (0xBC0) |

| #define | LOCIPRI1 (0xBC1) |

| #define | LOCIPRI2 (0xBC2) |

| #define | LOCIPRI3 (0xBC3) |

| #define | ICCTL (0x7C0) |

| #define | DCCTL (0x7C1) |

| #define | ICMAINT (0x7C2) |

| #define | DCMAINT (0x7C3) |

| #define | ICINVA (0x7C4) |

| #define | DCINCVA (0x7C5) |

| #define | MEMATTRL (0x7D8) |

| #define | MEMATTRH (0x7D9) |

| #define | LOCIPRI4 (0xBC4) |

| #define | LOCIPRI5 (0xBC5) |

| #define | LOCIPRI6 (0xBC6) |

| #define | LOCIPRI7 (0xBC7) |

| #define | LOCIPRI8 (0xBC8) |

| #define | LOCIPRI9 (0xBC9) |

| #define | LOCIPRI10 (0xBCA) |

| #define | LOCIPRI11 (0xBCB) |

| #define | LOCIPRI12 (0xBCC) |

| #define | LOCIPRI13 (0xBCD) |

| #define | LOCIPRI14 (0xBCE) |

| #define | LOCIPRI15 (0xBCF) |

| #define | locipri(x) LOCIPRI##x |

| #define | EXTERNAL_INTERRUPT_GROUP0 0 |

| #define | EXTERNAL_INTERRUPT_GROUP1 1 |

| #define | EXTERNAL_INTERRUPT_GROUP2 2 |

| #define | EXTERNAL_INTERRUPT_GROUP3 3 |

| #define | EXTERNAL_INTERRUPT_GROUP4 4 |

| #define | EXTERNAL_INTERRUPT_GROUP5 5 |

| #define | EXTERNAL_INTERRUPT_GROUP6 6 |

| #define | EXTERNAL_INTERRUPT_GROUP7 7 |

| #define | LOCIEN0 0xBE0 |

| #define | LOCIEN1 0xBE1 |

| #define | LOCIEN2 0xBE2 |

| #define | LOCIPD0 0xBE8 |

| #define | LOCIPD1 0xBE9 |

| #define | LOCIPD2 0xBEA |

| #define | LOCIPD3 0xBEB |

| #define | LOCIPCLR 0xBF0 |

| #define | PRITHD 0xBFE |

| #define | CXCPTSC 0xFC2 |

| #define | SIP_SSIP MIP_SSIP |

| #define | SIP_STIP MIP_STIP |

| #define | PRV_U 0 |

| #define | PRV_S 1 |

| #define | PRV_H 2 |

| #define | PRV_M 3 |

| #define | VM_MBARE 0 |

| #define | VM_MBB 1 |

| #define | VM_MBBID 2 |

| #define | VM_SV32 8 |

| #define | VM_SV39 9 |

| #define | VM_SV48 10 |

| #define | DEFAULT_RSTVEC 0x00001000 |

| #define | DEFAULT_NMIVEC 0x00001004 |

| #define | DEFAULT_MTVEC 0x00001010 |

| #define | CONFIG_STRING_ADDR 0x0000100C |

| #define | EXT_IO_BASE 0x40000000 |

| #define | DRAM_BASE 0x80000000 |

| #define | PTE_V 0x001 |

| #define | PTE_TYPE 0x01E |

| #define | PTE_R 0x020 |

| #define | PTE_D 0x040 |

| #define | PTE_SOFT 0x380 |

| #define | PTE_TYPE_TABLE 0x00 |

| #define | PTE_TYPE_TABLE_GLOBAL 0x02 |

| #define | PTE_TYPE_URX_SR 0x04 |

| #define | PTE_TYPE_URWX_SRW 0x06 |

| #define | PTE_TYPE_UR_SR 0x08 |

| #define | PTE_TYPE_URW_SRW 0x0A |

| #define | PTE_TYPE_URX_SRX 0x0C |

| #define | PTE_TYPE_URWX_SRWX 0x0E |

| #define | PTE_TYPE_SR 0x10 |

| #define | PTE_TYPE_SRW 0x12 |

| #define | PTE_TYPE_SRX 0x14 |

| #define | PTE_TYPE_SRWX 0x16 |

| #define | PTE_TYPE_SR_GLOBAL 0x18 |

| #define | PTE_TYPE_SRW_GLOBAL 0x1A |

| #define | PTE_TYPE_SRX_GLOBAL 0x1C |

| #define | PTE_TYPE_SRWX_GLOBAL 0x1E |

| #define | PTE_PPN_SHIFT 10 |

| #define | pte_table(pte) ((0x0000000AU >> ((pte) & 0x1F)) & 1) |

| #define | pte_ur(pte) ((0x0000AAA0U >> ((pte) & 0x1F)) & 1) |

| #define | pte_uw(pte) ((0x00008880U >> ((pte) & 0x1F)) & 1) |

| #define | pte_ux(pte) ((0x0000A0A0U >> ((pte) & 0x1F)) & 1) |

| #define | pte_sr(pte) ((0xAAAAAAA0U >> ((pte) & 0x1F)) & 1) |

| #define | pte_sw(pte) ((0x88888880U >> ((pte) & 0x1F)) & 1) |

| #define | pte_sx(pte) ((0xA0A0A000U >> ((pte) & 0x1F)) & 1) |

| #define | pte_check_perm(pte, supervisor, store, fetch) |

宏定义说明

◆ CONFIG_STRING_ADDR

| #define CONFIG_STRING_ADDR 0x0000100C |

◆ CXCPTSC

| #define CXCPTSC 0xFC2 |

◆ DCCTL

| #define DCCTL (0x7C1) |

◆ DCINCVA

| #define DCINCVA (0x7C5) |

◆ DCMAINT

| #define DCMAINT (0x7C3) |

◆ DEFAULT_MTVEC

| #define DEFAULT_MTVEC 0x00001010 |

◆ DEFAULT_NMIVEC

| #define DEFAULT_NMIVEC 0x00001004 |

◆ DEFAULT_RSTVEC

| #define DEFAULT_RSTVEC 0x00001000 |

◆ DRAM_BASE

| #define DRAM_BASE 0x80000000 |

◆ EXC_SIZE_ON_STACK

| #define EXC_SIZE_ON_STACK (160) |

◆ EXT_IO_BASE

| #define EXT_IO_BASE 0x40000000 |

◆ EXTERNAL_INTERRUPT_GROUP0

| #define EXTERNAL_INTERRUPT_GROUP0 0 |

◆ EXTERNAL_INTERRUPT_GROUP1

| #define EXTERNAL_INTERRUPT_GROUP1 1 |

◆ EXTERNAL_INTERRUPT_GROUP2

| #define EXTERNAL_INTERRUPT_GROUP2 2 |

◆ EXTERNAL_INTERRUPT_GROUP3

| #define EXTERNAL_INTERRUPT_GROUP3 3 |

◆ EXTERNAL_INTERRUPT_GROUP4

| #define EXTERNAL_INTERRUPT_GROUP4 4 |

◆ EXTERNAL_INTERRUPT_GROUP5

| #define EXTERNAL_INTERRUPT_GROUP5 5 |

◆ EXTERNAL_INTERRUPT_GROUP6

| #define EXTERNAL_INTERRUPT_GROUP6 6 |

◆ EXTERNAL_INTERRUPT_GROUP7

| #define EXTERNAL_INTERRUPT_GROUP7 7 |

◆ ICCTL

| #define ICCTL (0x7C0) |

◆ ICINVA

| #define ICINVA (0x7C4) |

◆ ICMAINT

| #define ICMAINT (0x7C2) |

◆ IRQ_COP

| #define IRQ_COP 12 |

◆ IRQ_H_EXT

| #define IRQ_H_EXT 10 |

◆ IRQ_H_SOFT

| #define IRQ_H_SOFT 2 |

◆ IRQ_H_TIMER

| #define IRQ_H_TIMER 6 |

◆ IRQ_HOST

| #define IRQ_HOST 13 |

◆ IRQ_LOCIE0

| #define IRQ_LOCIE0 26 |

◆ IRQ_LOCIE1

| #define IRQ_LOCIE1 27 |

◆ IRQ_LOCIE10

| #define IRQ_LOCIE10 4 |

◆ IRQ_LOCIE11

| #define IRQ_LOCIE11 5 |

◆ IRQ_LOCIE12

| #define IRQ_LOCIE12 6 |

◆ IRQ_LOCIE13

| #define IRQ_LOCIE13 7 |

◆ IRQ_LOCIE14

| #define IRQ_LOCIE14 8 |

◆ IRQ_LOCIE15

| #define IRQ_LOCIE15 9 |

◆ IRQ_LOCIE16

| #define IRQ_LOCIE16 10 |

◆ IRQ_LOCIE17

| #define IRQ_LOCIE17 11 |

◆ IRQ_LOCIE18

| #define IRQ_LOCIE18 12 |

◆ IRQ_LOCIE19

| #define IRQ_LOCIE19 13 |

◆ IRQ_LOCIE2

| #define IRQ_LOCIE2 28 |

◆ IRQ_LOCIE20

| #define IRQ_LOCIE20 14 |

◆ IRQ_LOCIE21

| #define IRQ_LOCIE21 15 |

◆ IRQ_LOCIE22

| #define IRQ_LOCIE22 16 |

◆ IRQ_LOCIE23

| #define IRQ_LOCIE23 17 |

◆ IRQ_LOCIE24

| #define IRQ_LOCIE24 18 |

◆ IRQ_LOCIE25

| #define IRQ_LOCIE25 19 |

◆ IRQ_LOCIE26

| #define IRQ_LOCIE26 20 |

◆ IRQ_LOCIE27

| #define IRQ_LOCIE27 21 |

◆ IRQ_LOCIE28

| #define IRQ_LOCIE28 22 |

◆ IRQ_LOCIE29

| #define IRQ_LOCIE29 23 |

◆ IRQ_LOCIE3

| #define IRQ_LOCIE3 29 |

◆ IRQ_LOCIE30

| #define IRQ_LOCIE30 24 |

◆ IRQ_LOCIE31

| #define IRQ_LOCIE31 25 |

◆ IRQ_LOCIE4

| #define IRQ_LOCIE4 30 |

◆ IRQ_LOCIE5

| #define IRQ_LOCIE5 31 |

◆ IRQ_LOCIE6

| #define IRQ_LOCIE6 0 |

◆ IRQ_LOCIE7

| #define IRQ_LOCIE7 1 |

◆ IRQ_LOCIE8

| #define IRQ_LOCIE8 2 |

◆ IRQ_LOCIE9

| #define IRQ_LOCIE9 3 |

◆ IRQ_M_EXT

| #define IRQ_M_EXT 11 |

◆ IRQ_M_SOFT

| #define IRQ_M_SOFT 3 |

◆ IRQ_M_TIMER

| #define IRQ_M_TIMER 7 |

◆ IRQ_NMI

| #define IRQ_NMI 12 |

◆ IRQ_S_EXT

| #define IRQ_S_EXT 9 |

◆ IRQ_S_SOFT

| #define IRQ_S_SOFT 1 |

◆ IRQ_S_TIMER

| #define IRQ_S_TIMER 5 |

◆ LOCIEN0

| #define LOCIEN0 0xBE0 |

◆ LOCIEN1

| #define LOCIEN1 0xBE1 |

◆ LOCIEN2

| #define LOCIEN2 0xBE2 |

◆ LOCIPCLR

| #define LOCIPCLR 0xBF0 |

◆ LOCIPD0

| #define LOCIPD0 0xBE8 |

◆ LOCIPD0_LOCIE10

| #define LOCIPD0_LOCIE10 (1 << IRQ_LOCIE10) |

◆ LOCIPD0_LOCIE11

| #define LOCIPD0_LOCIE11 (1 << IRQ_LOCIE11) |

◆ LOCIPD0_LOCIE12

| #define LOCIPD0_LOCIE12 (1 << IRQ_LOCIE12) |

◆ LOCIPD0_LOCIE13

| #define LOCIPD0_LOCIE13 (1 << IRQ_LOCIE13) |

◆ LOCIPD0_LOCIE14

| #define LOCIPD0_LOCIE14 (1 << IRQ_LOCIE14) |

◆ LOCIPD0_LOCIE15

| #define LOCIPD0_LOCIE15 (1 << IRQ_LOCIE15) |

◆ LOCIPD0_LOCIE16

| #define LOCIPD0_LOCIE16 (1 << IRQ_LOCIE16) |

◆ LOCIPD0_LOCIE17

| #define LOCIPD0_LOCIE17 (1 << IRQ_LOCIE17) |

◆ LOCIPD0_LOCIE18

| #define LOCIPD0_LOCIE18 (1 << IRQ_LOCIE18) |

◆ LOCIPD0_LOCIE19

| #define LOCIPD0_LOCIE19 (1 << IRQ_LOCIE19) |

◆ LOCIPD0_LOCIE20

| #define LOCIPD0_LOCIE20 (1 << IRQ_LOCIE20) |

◆ LOCIPD0_LOCIE21

| #define LOCIPD0_LOCIE21 (1 << IRQ_LOCIE21) |

◆ LOCIPD0_LOCIE22

| #define LOCIPD0_LOCIE22 (1 << IRQ_LOCIE22) |

◆ LOCIPD0_LOCIE23

| #define LOCIPD0_LOCIE23 (1 << IRQ_LOCIE23) |

◆ LOCIPD0_LOCIE24

| #define LOCIPD0_LOCIE24 (1 << IRQ_LOCIE24) |

◆ LOCIPD0_LOCIE25

| #define LOCIPD0_LOCIE25 (1 << IRQ_LOCIE25) |

◆ LOCIPD0_LOCIE26

| #define LOCIPD0_LOCIE26 (1 << IRQ_LOCIE26) |

◆ LOCIPD0_LOCIE27

| #define LOCIPD0_LOCIE27 (1 << IRQ_LOCIE27) |

◆ LOCIPD0_LOCIE28

| #define LOCIPD0_LOCIE28 (1 << IRQ_LOCIE28) |

◆ LOCIPD0_LOCIE29

| #define LOCIPD0_LOCIE29 (1 << IRQ_LOCIE29) |

◆ LOCIPD0_LOCIE30

| #define LOCIPD0_LOCIE30 (1 << IRQ_LOCIE30) |

◆ LOCIPD0_LOCIE31

| #define LOCIPD0_LOCIE31 (1 << IRQ_LOCIE31) |

◆ LOCIPD0_LOCIE6

| #define LOCIPD0_LOCIE6 (1 << IRQ_LOCIE6) |

◆ LOCIPD0_LOCIE7

| #define LOCIPD0_LOCIE7 (1 << IRQ_LOCIE7) |

◆ LOCIPD0_LOCIE8

| #define LOCIPD0_LOCIE8 (1 << IRQ_LOCIE8) |

◆ LOCIPD0_LOCIE9

| #define LOCIPD0_LOCIE9 (1 << IRQ_LOCIE9) |

◆ LOCIPD1

| #define LOCIPD1 0xBE9 |

◆ LOCIPD2

| #define LOCIPD2 0xBEA |

◆ LOCIPD3

| #define LOCIPD3 0xBEB |

◆ locipri

| #define locipri | ( | x | ) | LOCIPRI##x |

◆ LOCIPRI0

| #define LOCIPRI0 (0xBC0) |

◆ LOCIPRI1

| #define LOCIPRI1 (0xBC1) |

◆ LOCIPRI10

| #define LOCIPRI10 (0xBCA) |

◆ LOCIPRI11

| #define LOCIPRI11 (0xBCB) |

◆ LOCIPRI12

| #define LOCIPRI12 (0xBCC) |

◆ LOCIPRI13

| #define LOCIPRI13 (0xBCD) |

◆ LOCIPRI14

| #define LOCIPRI14 (0xBCE) |

◆ LOCIPRI15

| #define LOCIPRI15 (0xBCF) |

◆ LOCIPRI2

| #define LOCIPRI2 (0xBC2) |

◆ LOCIPRI3

| #define LOCIPRI3 (0xBC3) |

◆ LOCIPRI4

| #define LOCIPRI4 (0xBC4) |

◆ LOCIPRI5

| #define LOCIPRI5 (0xBC5) |

◆ LOCIPRI6

| #define LOCIPRI6 (0xBC6) |

◆ LOCIPRI7

| #define LOCIPRI7 (0xBC7) |

◆ LOCIPRI8

| #define LOCIPRI8 (0xBC8) |

◆ LOCIPRI9

| #define LOCIPRI9 (0xBC9) |

◆ MCAUSE

| #define MCAUSE 0x342 |

◆ MCAUSE32_CAUSE

| #define MCAUSE32_CAUSE 0x7FFFFFFF |

◆ MCAUSE32_INT

| #define MCAUSE32_INT 0x80000000 |

◆ MCAUSE64_CAUSE

| #define MCAUSE64_CAUSE 0x7FFFFFFFFFFFFFFF |

◆ MCAUSE64_INT

| #define MCAUSE64_INT 0x8000000000000000 |

◆ MCAUSE_AMO_FAULT

| #define MCAUSE_AMO_FAULT 0x7 |

◆ MCAUSE_AMO_MISALIGN

| #define MCAUSE_AMO_MISALIGN 0x6 |

◆ MCAUSE_AMO_PAGE_FAULT

| #define MCAUSE_AMO_PAGE_FAULT 0xF |

◆ MCAUSE_BRKT

| #define MCAUSE_BRKT 0x3 |

◆ MCAUSE_ECALL_M

| #define MCAUSE_ECALL_M 0xB |

◆ MCAUSE_ECALL_U

| #define MCAUSE_ECALL_U 0x8 |

◆ MCAUSE_INSN_FAULT

| #define MCAUSE_INSN_FAULT 0x1 |

◆ MCAUSE_INSN_ILLEGAL

| #define MCAUSE_INSN_ILLEGAL 0x2 |

◆ MCAUSE_INSN_MISALIGN

| #define MCAUSE_INSN_MISALIGN 0x0 |

◆ MCAUSE_INSN_PAGE_FAULT

| #define MCAUSE_INSN_PAGE_FAULT 0xC |

◆ MCAUSE_LOAD_FAULT

| #define MCAUSE_LOAD_FAULT 0x5 |

◆ MCAUSE_LOAD_PAGE_FAULT

| #define MCAUSE_LOAD_PAGE_FAULT 0xD |

◆ MCSUSE_LOAD_MISALIGN

| #define MCSUSE_LOAD_MISALIGN 0x4 |

◆ MEMATTRH

| #define MEMATTRH (0x7D9) |

◆ MEMATTRL

| #define MEMATTRL (0x7D8) |

◆ MIP_HEIE

| #define MIP_HEIE (1 << IRQ_H_EXT) |

◆ MIP_HSIE

| #define MIP_HSIE (1 << IRQ_H_SOFT) |

◆ MIP_HTIE

| #define MIP_HTIE (1 << IRQ_H_TIMER) |

◆ MIP_LOCIE0

| #define MIP_LOCIE0 (1 << IRQ_LOCIE0) |

◆ MIP_LOCIE1

| #define MIP_LOCIE1 (1 << IRQ_LOCIE1) |

◆ MIP_LOCIE2

| #define MIP_LOCIE2 (1 << IRQ_LOCIE2) |

◆ MIP_LOCIE3

| #define MIP_LOCIE3 (1 << IRQ_LOCIE3) |

◆ MIP_LOCIE4

| #define MIP_LOCIE4 (1 << IRQ_LOCIE4) |

◆ MIP_LOCIE5

| #define MIP_LOCIE5 ((uint32_t)1 << IRQ_LOCIE5) |

◆ MIP_MEIE

| #define MIP_MEIE (1 << IRQ_M_EXT) |

◆ MIP_MSIE

| #define MIP_MSIE (1 << IRQ_M_SOFT) |

◆ MIP_MTIE

| #define MIP_MTIE (1 << IRQ_M_TIMER) |

◆ MIP_NMI

| #define MIP_NMI (1 << IRQ_NMI) |

◆ MIP_NMIE

| #define MIP_NMIE (1 << IRQ_COP) |

◆ MIP_SEIE

| #define MIP_SEIE (1 << IRQ_S_EXT) |

◆ MIP_SSIE

| #define MIP_SSIE (1 << IRQ_S_SOFT) |

◆ MIP_STIE

| #define MIP_STIE (1 << IRQ_S_TIMER) |

◆ MSTATUS32_SD

| #define MSTATUS32_SD 0x80000000 |

◆ MSTATUS64_SD

| #define MSTATUS64_SD 0x8000000000000000 |

◆ MSTATUS_FS

| #define MSTATUS_FS 0x00006000 |

◆ MSTATUS_HIE

| #define MSTATUS_HIE 0x00000004 |

◆ MSTATUS_HPIE

| #define MSTATUS_HPIE 0x00000040 |

◆ MSTATUS_HPP

| #define MSTATUS_HPP 0x00000600 |

◆ MSTATUS_MIE

| #define MSTATUS_MIE 0x00000008 |

◆ MSTATUS_MPIE

| #define MSTATUS_MPIE 0x00000080 |

◆ MSTATUS_MPP

| #define MSTATUS_MPP 0x00001800 |

◆ MSTATUS_MPRV

| #define MSTATUS_MPRV 0x00020000 |

◆ MSTATUS_PUM

| #define MSTATUS_PUM 0x00040000 |

◆ MSTATUS_SIE

| #define MSTATUS_SIE 0x00000002 |

◆ MSTATUS_SPIE

| #define MSTATUS_SPIE 0x00000020 |

◆ MSTATUS_SPP

| #define MSTATUS_SPP 0x00000100 |

◆ MSTATUS_UIE

| #define MSTATUS_UIE 0x00000001 |

◆ MSTATUS_UPIE

| #define MSTATUS_UPIE 0x00000010 |

◆ MSTATUS_VM

| #define MSTATUS_VM 0x1F000000 |

◆ MSTATUS_XS

| #define MSTATUS_XS 0x00018000 |

◆ PMPADDR0

| #define PMPADDR0 0 |

◆ PMPADDR1

| #define PMPADDR1 1 |

◆ PMPADDR10

| #define PMPADDR10 10 |

◆ PMPADDR11

| #define PMPADDR11 11 |

◆ PMPADDR12

| #define PMPADDR12 12 |

◆ PMPADDR13

| #define PMPADDR13 13 |

◆ PMPADDR14

| #define PMPADDR14 14 |

◆ PMPADDR15

| #define PMPADDR15 15 |

◆ PMPADDR2

| #define PMPADDR2 2 |

◆ PMPADDR3

| #define PMPADDR3 3 |

◆ PMPADDR4

| #define PMPADDR4 4 |

◆ PMPADDR5

| #define PMPADDR5 5 |

◆ PMPADDR6

| #define PMPADDR6 6 |

◆ PMPADDR7

| #define PMPADDR7 7 |

◆ PMPADDR8

| #define PMPADDR8 8 |

◆ PMPADDR9

| #define PMPADDR9 9 |

◆ PMPCFG0

| #define PMPCFG0 0 |

◆ PMPCFG1

| #define PMPCFG1 1 |

◆ PMPCFG2

| #define PMPCFG2 2 |

◆ PMPCFG3

| #define PMPCFG3 3 |

◆ PRITHD

| #define PRITHD 0xBFE |

◆ PRV_H

| #define PRV_H 2 |

◆ PRV_M

| #define PRV_M 3 |

◆ PRV_S

| #define PRV_S 1 |

◆ PRV_U

| #define PRV_U 0 |

◆ pte_check_perm

| #define pte_check_perm | ( | pte, | |

| supervisor, | |||

| store, | |||

| fetch | |||

| ) |

值:

◆ PTE_D

| #define PTE_D 0x040 |

◆ PTE_PPN_SHIFT

| #define PTE_PPN_SHIFT 10 |

◆ PTE_R

| #define PTE_R 0x020 |

◆ PTE_SOFT

| #define PTE_SOFT 0x380 |

◆ pte_sr

| #define pte_sr | ( | pte | ) | ((0xAAAAAAA0U >> ((pte) & 0x1F)) & 1) |

◆ pte_sw

| #define pte_sw | ( | pte | ) | ((0x88888880U >> ((pte) & 0x1F)) & 1) |

◆ pte_sx

| #define pte_sx | ( | pte | ) | ((0xA0A0A000U >> ((pte) & 0x1F)) & 1) |

◆ pte_table

| #define pte_table | ( | pte | ) | ((0x0000000AU >> ((pte) & 0x1F)) & 1) |

◆ PTE_TYPE

| #define PTE_TYPE 0x01E |

◆ PTE_TYPE_SR

| #define PTE_TYPE_SR 0x10 |

◆ PTE_TYPE_SR_GLOBAL

| #define PTE_TYPE_SR_GLOBAL 0x18 |

◆ PTE_TYPE_SRW

| #define PTE_TYPE_SRW 0x12 |

◆ PTE_TYPE_SRW_GLOBAL

| #define PTE_TYPE_SRW_GLOBAL 0x1A |

◆ PTE_TYPE_SRWX

| #define PTE_TYPE_SRWX 0x16 |

◆ PTE_TYPE_SRWX_GLOBAL

| #define PTE_TYPE_SRWX_GLOBAL 0x1E |

◆ PTE_TYPE_SRX

| #define PTE_TYPE_SRX 0x14 |

◆ PTE_TYPE_SRX_GLOBAL

| #define PTE_TYPE_SRX_GLOBAL 0x1C |

◆ PTE_TYPE_TABLE

| #define PTE_TYPE_TABLE 0x00 |

◆ PTE_TYPE_TABLE_GLOBAL

| #define PTE_TYPE_TABLE_GLOBAL 0x02 |

◆ PTE_TYPE_UR_SR

| #define PTE_TYPE_UR_SR 0x08 |

◆ PTE_TYPE_URW_SRW

| #define PTE_TYPE_URW_SRW 0x0A |

◆ PTE_TYPE_URWX_SRW

| #define PTE_TYPE_URWX_SRW 0x06 |

◆ PTE_TYPE_URWX_SRWX

| #define PTE_TYPE_URWX_SRWX 0x0E |

◆ PTE_TYPE_URX_SR

| #define PTE_TYPE_URX_SR 0x04 |

◆ PTE_TYPE_URX_SRX

| #define PTE_TYPE_URX_SRX 0x0C |

◆ pte_ur

| #define pte_ur | ( | pte | ) | ((0x0000AAA0U >> ((pte) & 0x1F)) & 1) |

◆ pte_uw

| #define pte_uw | ( | pte | ) | ((0x00008880U >> ((pte) & 0x1F)) & 1) |

◆ pte_ux

| #define pte_ux | ( | pte | ) | ((0x0000A0A0U >> ((pte) & 0x1F)) & 1) |

◆ PTE_V

| #define PTE_V 0x001 |

◆ SIP_SSIP

| #define SIP_SSIP MIP_SSIP |

◆ SIP_STIP

| #define SIP_STIP MIP_STIP |

◆ SSTATUS32_SD

| #define SSTATUS32_SD 0x80000000 |

◆ SSTATUS64_SD

| #define SSTATUS64_SD 0x8000000000000000 |

◆ SSTATUS_FS

| #define SSTATUS_FS 0x00006000 |

◆ SSTATUS_PUM

| #define SSTATUS_PUM 0x00040000 |

◆ SSTATUS_SIE

| #define SSTATUS_SIE 0x00000002 |

◆ SSTATUS_SPIE

| #define SSTATUS_SPIE 0x00000020 |

◆ SSTATUS_SPP

| #define SSTATUS_SPP 0x00000100 |

◆ SSTATUS_UIE

| #define SSTATUS_UIE 0x00000001 |

◆ SSTATUS_UPIE

| #define SSTATUS_UPIE 0x00000010 |

◆ SSTATUS_XS

| #define SSTATUS_XS 0x00018000 |

◆ VM_MBARE

| #define VM_MBARE 0 |

◆ VM_MBB

| #define VM_MBB 1 |

◆ VM_MBBID

| #define VM_MBBID 2 |

◆ VM_SV32

| #define VM_SV32 8 |

◆ VM_SV39

| #define VM_SV39 9 |

◆ VM_SV48

| #define VM_SV48 10 |